# Advanced 8-bit Micro-controller with 171K Flash ROM and Dual CAN controllers

# **CS8959**

Advanced 8-bit Micro-controller with 171K Flash ROM and Dual CAN controllers

Ver. 0.91

# **Topic of Contents**

| 1.  | GEN  | <b>ERAL D</b>  | DESCRIPTION                                      |          |

|-----|------|----------------|--------------------------------------------------|----------|

| 2.  |      | TURES.         |                                                  |          |

| 3.  | BLO  | CK DIA         | GRAM                                             |          |

| 4.  |      |                | CTION                                            |          |

| 5.  |      |                | PTION                                            |          |

| 6.  |      |                | LLOCATION                                        |          |

| 0.  | 6.1  | INITED         | NAL SPECIAL FUNCTION REGISTERS (SFR)             |          |

|     | 6.2  | INTER          | VAL OF ECIAL FONCTION REGISTERS (SFR)            | 10<br>16 |

|     | 6.3  | FXTFR          | NAL SPECIAL FUNCTION REGISTERS (XFR)             | 16       |

|     | 6.4  |                | EGISTERS                                         |          |

|     | 6.5  | AUXILI         | ARY RAM (AUXRAM)                                 | 16       |

| 7.  | MEN  | IORY M         | AP OF XFR (0X0F000X0FFF)                         | 17       |

|     | 7.1  |                | ONFIGURATION                                     |          |

| 8.  | CS89 | 959 SFR        | RALLOCATION                                      | 22       |

|     | 8.1  | INTRO          | DUCTION                                          | 22       |

|     | 8.2  | INTERN         | NAL DATA MEMORY & SFRS ALLOCATION                | 22       |

| 9.  | SPE  | CIAL SF        | R DEFINITION                                     | 24       |

|     | 9.1  |                | RAM WAIT STATES REGISTER                         |          |

|     |      |                | Wait-states Cycle Register (default 0X00)        |          |

|     |      |                | WTST Register Values                             |          |

|     | 9.2  |                | ARGE MODEL SWITCHING                             |          |

|     |      | 9.2.1          | Address Control Register                         |          |

|     |      | 9.2.2<br>9.2.3 | Address Control                                  |          |

|     | 9.3  |                | Stack Pointer RegisterPOINTER EXTENDED REGISTERS |          |

|     | 9.3  | 9.3.1          | Data Pointer Extended Register                   |          |

|     |      | 9.3.2          | Data Pointer Extended 1 Register                 |          |

|     |      | 9.3.3          | MOVX @Ri Extended High Register                  |          |

|     |      | 9.3.4          | MOVX @Ri Extended Middle Register                |          |

|     | 9.4  | RESER          | RVED REGISTER                                    |          |

|     | 9.5  | DATA F         | POINTER REGISTER                                 |          |

|     |      | 9.5.1          | Data Pointer Register DPTR (default 0X0000)      |          |

|     |      | 9.5.2          | Data Pointer 1 Register DPTR1 (default 0X0000)   |          |

|     |      | 9.5.3          | Data pointer Select Register                     | 27       |

|     | 9.6  |                | CONTROL REGISTER-STRETCH BITS                    |          |

|     |      | 9.6.1          | Clock Control Register                           |          |

|     | 9.7  |                | ACCESS REGISTERS                                 |          |

|     | 9.1  | 9.7.1          | Timed Access Registers                           |          |

| 10. | INTE | -              | SYSTEM                                           |          |

| 10. | 10.1 |                | RUPT VECTOR                                      | _        |

|     | 10.1 | 10.1.1         | Interrupt Enable Register                        |          |

|     |      | 10.1.2         | Interrupt Priority Register                      |          |

|     |      | 10.1.3         | External Interrupt Enable Register               |          |

|     |      | 10.1.4         | External Interrupt Priority Register             |          |

|     |      | 10.1.5         | External Interrupt Flag Register                 | 31       |

|     |      | 10.1.6         | Timer 0,1 Configuration Register                 |          |

|     |      | 10.1.7         | Timer 2 Configuration Register                   |          |

|     |      | 10.1.8         | UARTO Configuration Register                     |          |

|     |      | 10.1.9         | UART1Configuration Register                      |          |

| 4.4 | D014 | 10.1.10        | , ,                                              |          |

| 11. |      |                | VING UNIT                                        |          |

|     | 11.1 | 11.1.1         | odeStop Bit Power Configuration Pegister         |          |

|     |      | 11.1.1         | Stop Bit Power Configuration Register            | 33       |

|     | 11.2 | Power Manag  | gement Mode                                           | 36 |

|-----|------|--------------|-------------------------------------------------------|----|

|     |      | 11.2.1       | Power Management Register                             | 36 |

|     |      | 11.2.2       | Status Register                                       |    |

|     |      | 11.2.3       | Power Management Related Bit                          | 37 |

|     | 11.3 | Low Power M  | Mode                                                  | 37 |

|     | 11.4 |              | ripherals                                             |    |

|     | 11.5 | Switchback F | eature                                                | 38 |

|     | 11.6 | Switchback F | eature Timing                                         | 39 |

|     | 11.7 | Pulse Mode   | -                                                     | 39 |

| 12. | TIME | RS           |                                                       | 40 |

|     | 12.1 | Timer 0 And  | Timer 1                                               | 40 |

|     |      | 12.1.1       | Timer 0,Timer1 Modes                                  |    |

|     |      | 12.1.2       | Timer 0, Timer1 Control Mode Register                 |    |

|     |      | 12.1.3       | Timer 0, Timer1 Configuration Register                |    |

|     |      | 12.1.4       | Clock Control Register                                |    |

|     | 12.2 | Timer 0 Oper | ration                                                |    |

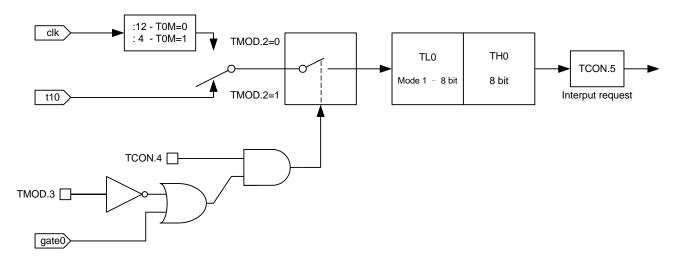

|     |      | 12.2.1       | Mode 0                                                |    |

|     |      | 12.2.2       | Mode 1                                                |    |

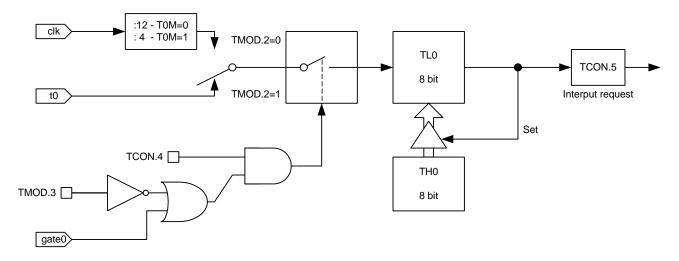

|     |      | 12.2.3       | Mode 2                                                |    |

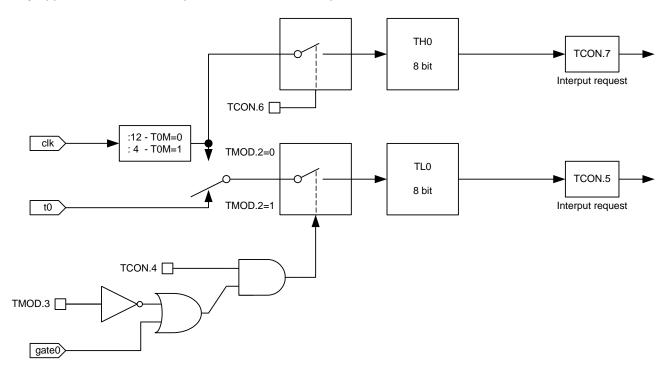

|     |      | 12.2.4       | Mode 3                                                | 43 |

|     | 12.3 | Timer 1 Oper | ration                                                |    |

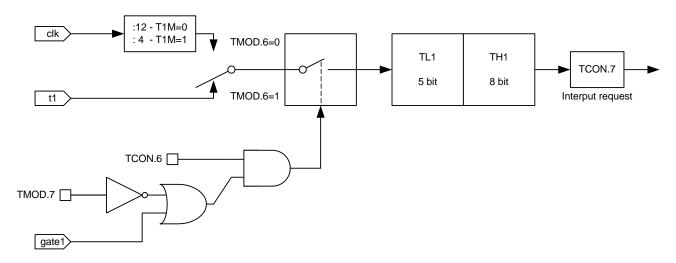

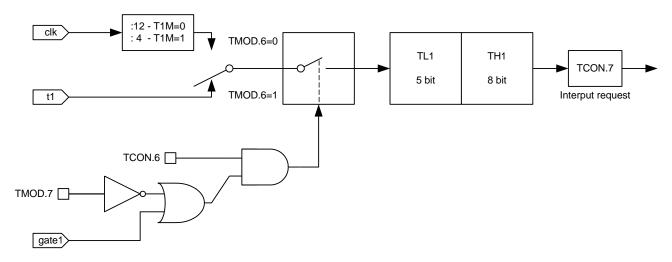

|     |      | 12.3.1       | Mode 0                                                | 44 |

|     |      | 12.3.2       | Mode 1                                                | 44 |

|     |      | 12.3.3       | Mode 2                                                | 45 |

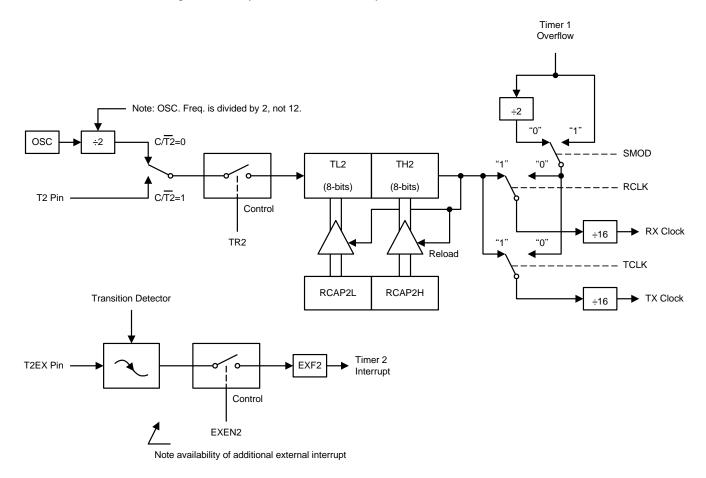

|     | 12.4 | Timer 2 Oper | ration                                                | 45 |

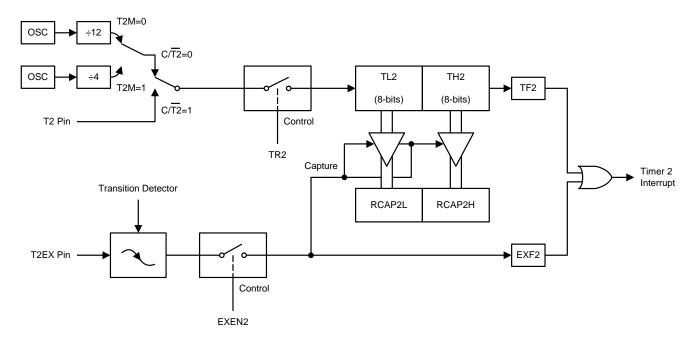

|     |      | 12.4.1       | Capture Mode                                          | 45 |

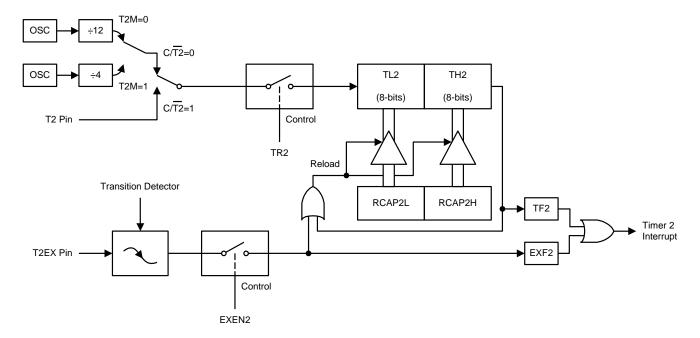

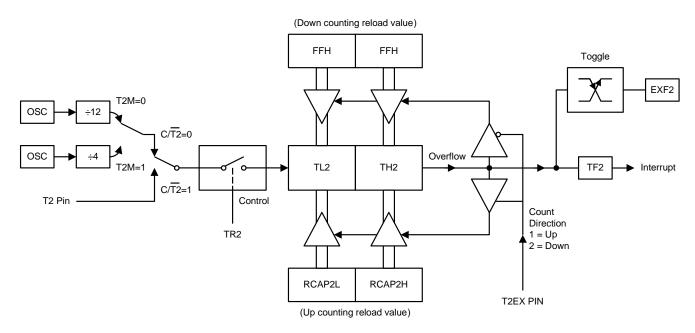

|     |      | 12.4.2       | Auto-Reload Mode (Up or Down Counter)                 | 47 |

|     |      | 12.4.3       | Baud Rate Generator Mode                              | 49 |

| 13. | SER  | IAL PORTS    | (UARTS)                                               | 50 |

|     | 13.1 |              |                                                       |    |

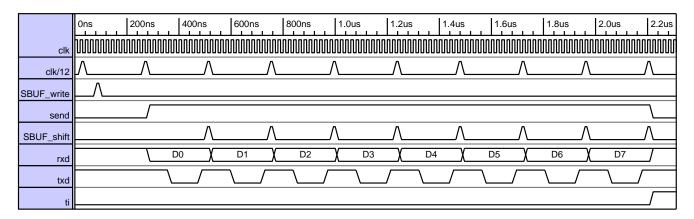

|     |      | 13.1.1       | MODE 0, SYNCHRONOUS                                   |    |

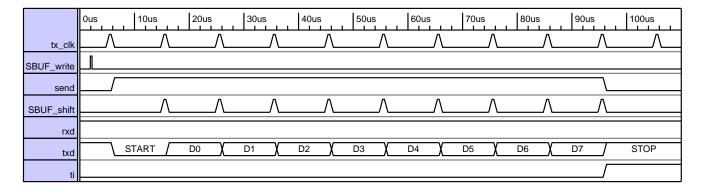

|     |      | 13.1.2       | MODE 1, 8-BIT UART, VARIABLE BAUD RATE, TIMER 1 OR 2  | _  |

|     |      | CLOCK SOU    | IRCES                                                 | 52 |

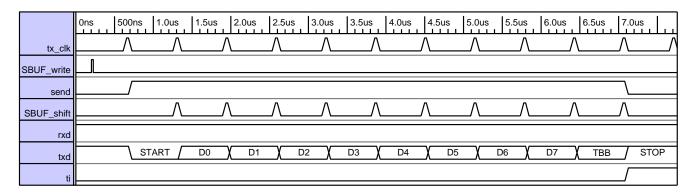

|     |      | 13.1.3       | MODE 2, 9-BIT UART, FIXED BAUD RATE                   |    |

|     |      | 13.1.4       | MODE 3, 9-BIT UART, VARIABLE BAUD RATE, TIMER 1 OR 2  |    |

|     |      | CLOCK SOU    | IRCES                                                 | 53 |

|     | 13.2 | UART1        |                                                       | 54 |

|     |      | 13.2.1       | MODE 0, SYNCHRONOUS                                   |    |

|     |      | 13.2.2       | MODE 1, 8-BIT UART, VARIABLE BAUD RATE, TIMER 1 CLOCK |    |

|     |      | SOURCE       | 56                                                    |    |

|     |      | 13.2.3       | MODE 2, 9-BIT UART, FIXED BAUD RATE                   | 56 |

|     |      | 13.2.4       | MODE 3, 9-BIT UART, VARIABLE BAUD RATE, TIMER 1 CLOCK |    |

|     |      | SOURCE       | 57                                                    |    |

| 14. | MDU  | - MULTIPL    | ICATION AND DIVISION UNIT                             | 58 |

|     | 14.1 |              | Multiplication Operations                             |    |

|     |      | 14.1.1       | WRITE SEQUENCE                                        |    |

|     |      | 14.1.2       | READ SEQUENCE                                         |    |

|     | 14.2 |              | peration                                              |    |

|     |      | 14.2.1       | WRITE SEQUENCE                                        |    |

|     |      | 14.2.2       | READ SEQUENCE                                         |    |

|     | 14.3 |              | on                                                    |    |

|     |      | 14.3.1       | WRITE SEQUENCE                                        |    |

|     |      | 14.3.2       | READ SEQUENCE                                         |    |

|     | 14.4 | -            | lag                                                   |    |

|     | 14.5 |              | w Flag                                                |    |

| 15. |      |              | R IIC BUS CONTROLLER                                  |    |

| 13. | 15.1 |              | Short Specification                                   |    |

|     | 13.1 | 15.1.1       | THE I2C-BUS CONCEPT                                   |    |

|     |      | 10.1.1       |                                                       | 02 |

|     |      | 15.1.2           | TRANSFERRING DATA                     | 63  |

|-----|------|------------------|---------------------------------------|-----|

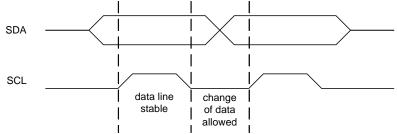

|     |      | 15.1.3           | BIT TRANSFER                          | 63  |

|     |      | 15.1.4           | DATA VALIDITY                         |     |

|     |      | 15.1.5           | START AND STOP CONDITIONS             | 64  |

|     |      | 15.1.6           | BYTE FORMAT                           |     |

|     |      | 15.1.7           | ACKNOWLEDGE                           |     |

|     |      | 15.1.8           | CLOCK SYNCHRONIZATION                 |     |

|     |      | 15.1.9           | ARBITRATION                           | 65  |

|     |      | 15.1.10          | DATA FORMAT WITH 7-BIT ADDRESS        |     |

|     | 15.2 |                  | egisters                              | 66  |

|     |      | 15.2.1           | I2CMTP - TIMER PERIOD REGISTER        | 66  |

|     |      | 15.2.2           | I2CMCR - CONTROL AND STATUS REGISTERS |     |

|     | 45.0 | 15.2.3           | I2CMSA - SLAVE ADDRESS REGISTER       |     |

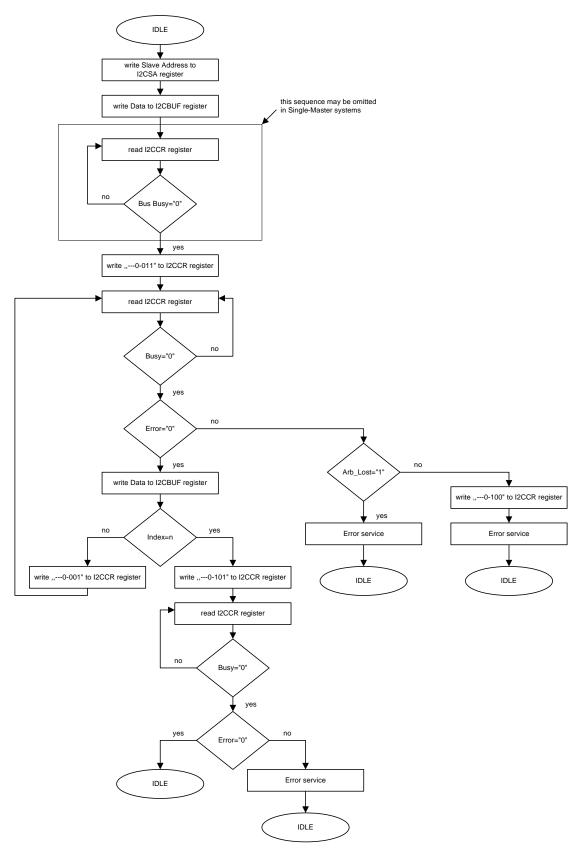

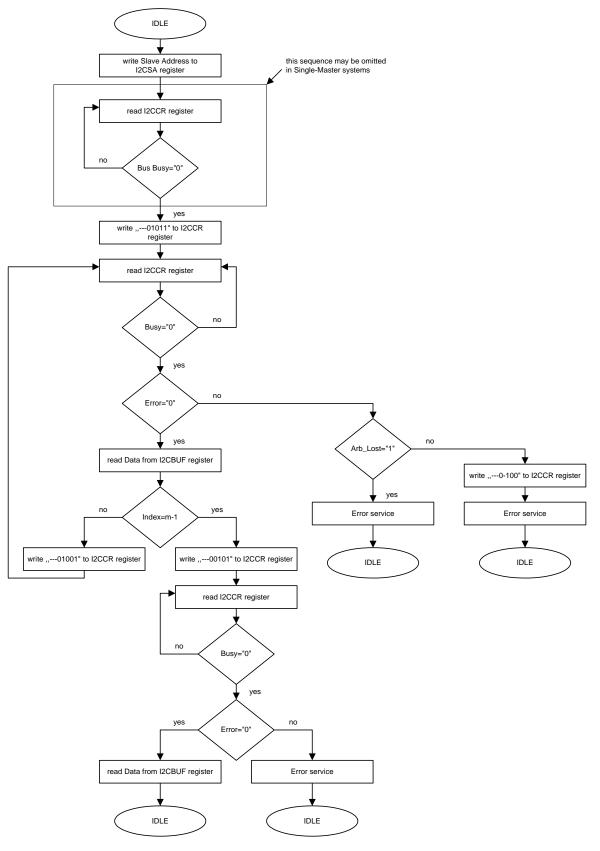

|     | 15.3 |                  | Command Sequences                     |     |

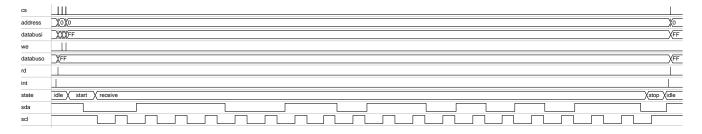

|     |      | 15.3.1           | SINGLE SEND                           |     |

|     |      | 15.3.2           | SINGLE RECEIVE                        |     |

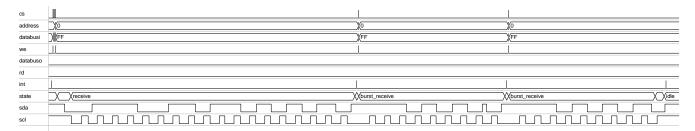

|     |      | 15.3.3<br>15.3.4 | BURST SEND<br>BURST RECEIVE           |     |

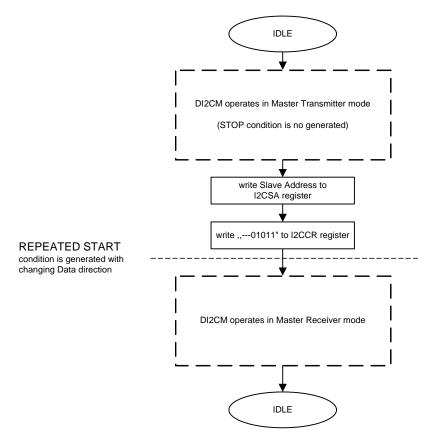

|     |      | 15.3.4           | BURST RECEIVE AFTER BURST SEND        |     |

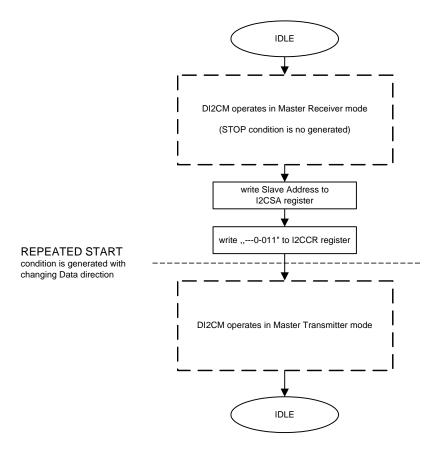

|     |      | 15.3.6           | BURST SEND AFTER BURST RECEIVE        |     |

| 16. | CI A | VE IIC           |                                       |     |

| 10. | 16.1 |                  | IIC And Slave B 1 IIC                 |     |

|     | 16.1 |                  | IIC XFR                               |     |

|     | 16.2 |                  | IIC XFR                               |     |

| 17. |      |                  | IIO AFK                               |     |

| 17. |      |                  |                                       |     |

| 40  | 17.1 |                  | g Illustration                        |     |

| 18. |      |                  |                                       |     |

|     | 18.1 |                  |                                       |     |

|     | 18.2 |                  | )                                     |     |

| 19. |      |                  | IMER                                  |     |

|     | 19.1 |                  | Timer Reset                           |     |

|     | 19.2 | •                | mer                                   |     |

|     | 19.3 |                  | onitor                                |     |

|     | 19.4 | _                | Related Registers                     |     |

|     |      | 19.4.1           | WATCHDOG CONTROL                      |     |

|     | DTO  | 19.4.2           | CLOCK CONTROL                         |     |

| 20. |      |                  | ON                                    |     |

|     | 20.1 |                  | IE CLOCK                              |     |

|     | 20.2 |                  | sters Configure                       |     |

|     | 20.3 |                  | Timer                                 |     |

| •   | 20.4 |                  | ster Definitions                      |     |

| 21. |      | 1 DAC            |                                       |     |

| 22. | LOW  | / VOLTAG         | E DETECTION                           |     |

| 23. | ECT  |                  |                                       | 103 |

|     | 23.1 | ECT0             |                                       | 103 |

|     |      | 23.1.1           | Capture Mode                          | 104 |

|     |      | 23.1.2           | Auto-Reload Mode                      | 105 |

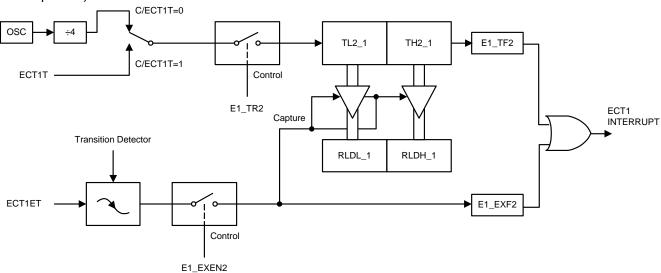

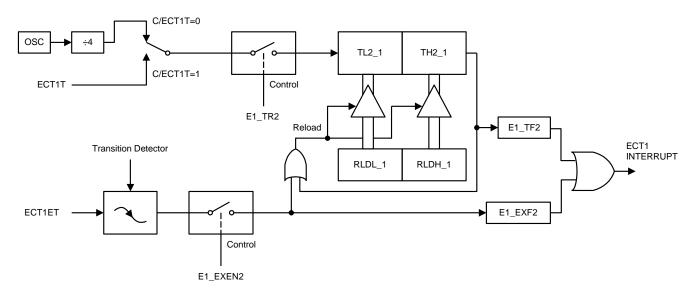

|     | 23.2 | ECT1             |                                       |     |

|     |      | 23.2.1           | Capture Mode                          | 107 |

|     |      | 23.2.2           | Auto-Reload Mode                      |     |

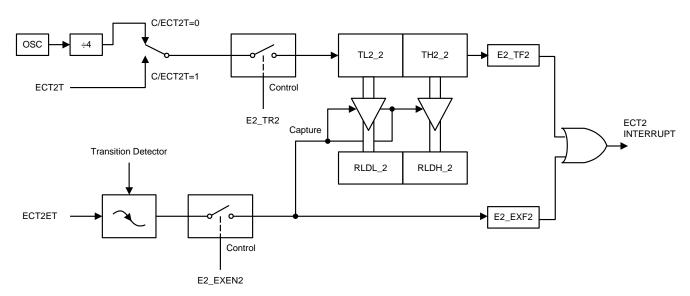

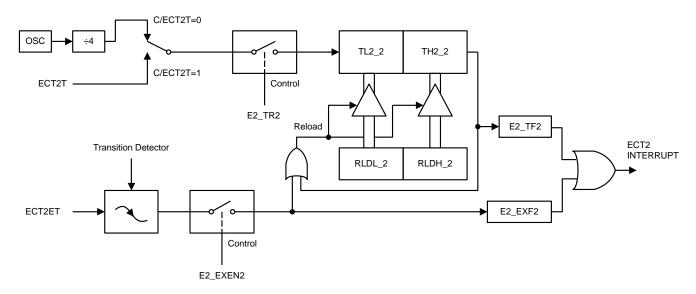

|     | 23.3 | ECT2             |                                       |     |

|     |      | 23.3.1           | Capture Mode                          |     |

|     |      | 23.3.2           | Auto-Reload Mode                      |     |

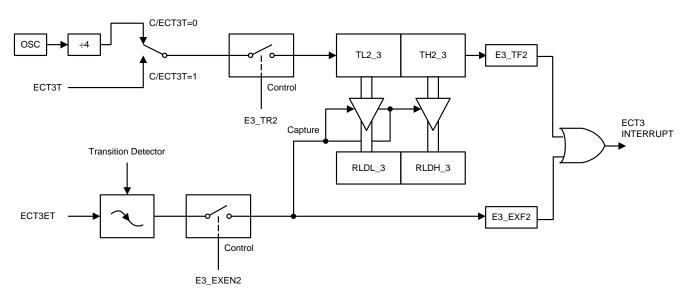

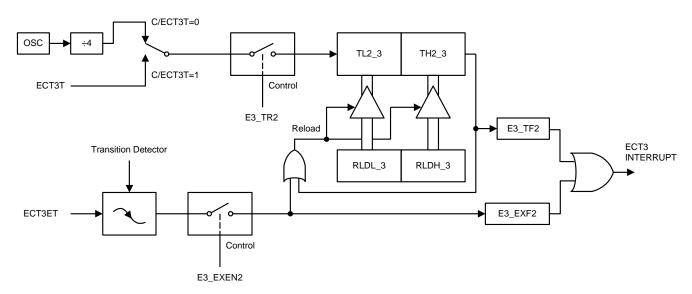

|     | 23.4 | ECT3             |                                       |     |

|     |      | 23.4.1           | Capture Mode                          |     |

|     |      | 23.4.2           | Auto-Reload Mode                      |     |

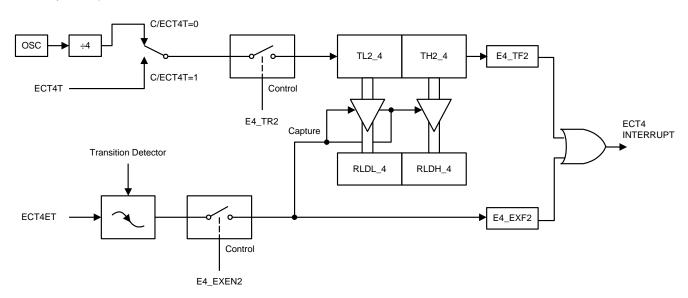

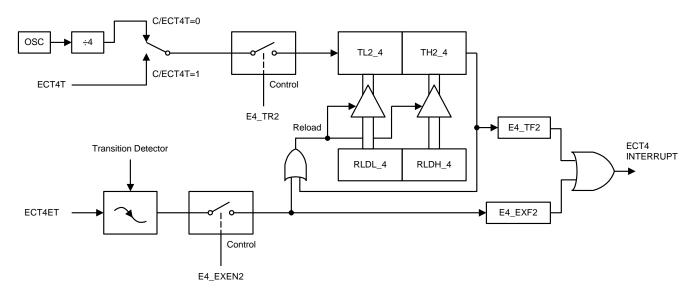

|     | 23.5 | ECT4             |                                       | 115 |

|     |      | 23.5.1     | Capture Mode                                     | 116 |

|-----|------|------------|--------------------------------------------------|-----|

|     |      | 23.5.2     | Auto-Reload Mode                                 | 117 |

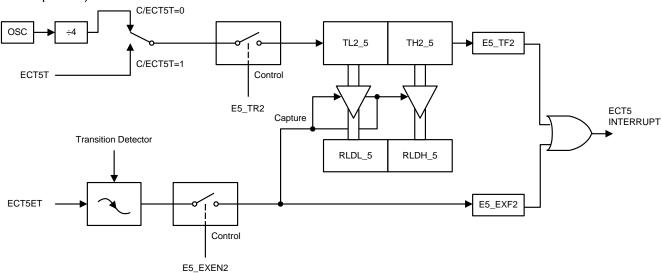

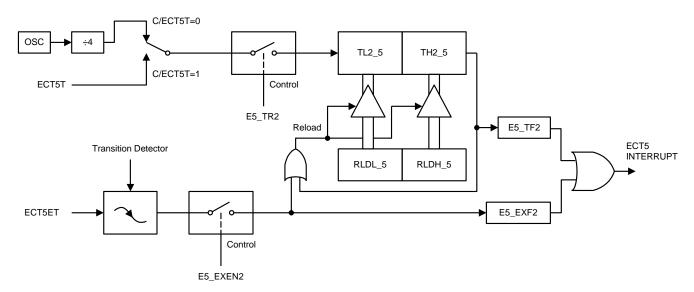

|     | 23.6 | ECT5       |                                                  | 118 |

|     |      | 23.6.1     | Capture Mode                                     | 119 |

|     |      | 23.6.2     | Auto-Reload Mode                                 |     |

| 24. | BUF  | FERED CL   | OCK OUTPUT                                       |     |

| 25. |      |            | NTROLLER                                         |     |

| 26. |      |            | LER                                              |     |

|     | 26.1 |            | oller Function Description                       |     |

|     | 26.2 |            | Description                                      |     |

|     |      | 26.2.1     | Registers mapping                                |     |

|     |      | 26.2.2     | Registers Function Description                   |     |

|     | 26.3 | Basic Func | tion                                             |     |

|     |      | 26.3.1     | Pin Configuration                                |     |

|     |      | 26.3.2     | Proper setting of Operating mode and Silent mode |     |

|     |      | 26.3.3     | Proper setting of Baud Rate                      | 156 |

|     |      | 26.3.4     | The setting of the acceptance filter             |     |

|     |      | 26.3.5     | The setting of Interrupt                         | 160 |

|     |      | 26.3.6     | Transmitting a frame                             | 160 |

|     |      | 26.3.7     | Receiving a frame                                | 160 |

|     | 26.4 | Advanced I | Function                                         | 161 |

|     |      | 26.4.1     | Dispatch                                         | 161 |

|     |      | 26.4.2     | Forward                                          | 161 |

|     | 26.5 | CAN Test   |                                                  | 162 |

|     |      | 26.5.1     | Self-Loop Test                                   | 162 |

|     |      | 26.5.2     | Dual loop test                                   |     |

| 27. | ELE( | CTRICAL C  | CHARACTERISTICS                                  | 164 |

|     | 27.1 | Absolute M | laximum Rating                                   | 164 |

|     | 27.2 | Recommen   | nd Operating Condition                           | 164 |

|     | 27.3 | DC/AC Ele  | ctrical Characteristics                          | 164 |

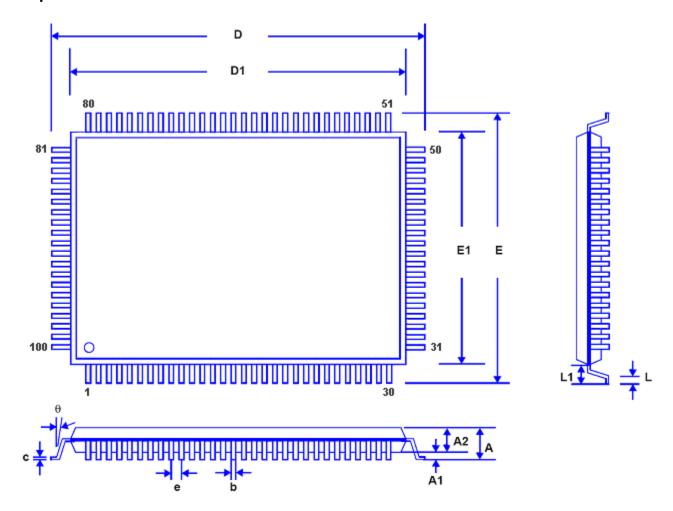

| 28. | PAC  | KAGE OUT   | TLINE                                            | 165 |

|     | 28.1 |            | outline                                          |     |

| 29. | ORD  | •          | ORMATION                                         |     |

# **Topic of Diagrams**

| Figure-1.  | Block Diagram                                                              |     |

|------------|----------------------------------------------------------------------------|-----|

| Figure-2.  | Package Type                                                               |     |

| Figure-3.  | Auxiliary RAM                                                              |     |

| Figure-4.  | SFR Map                                                                    |     |

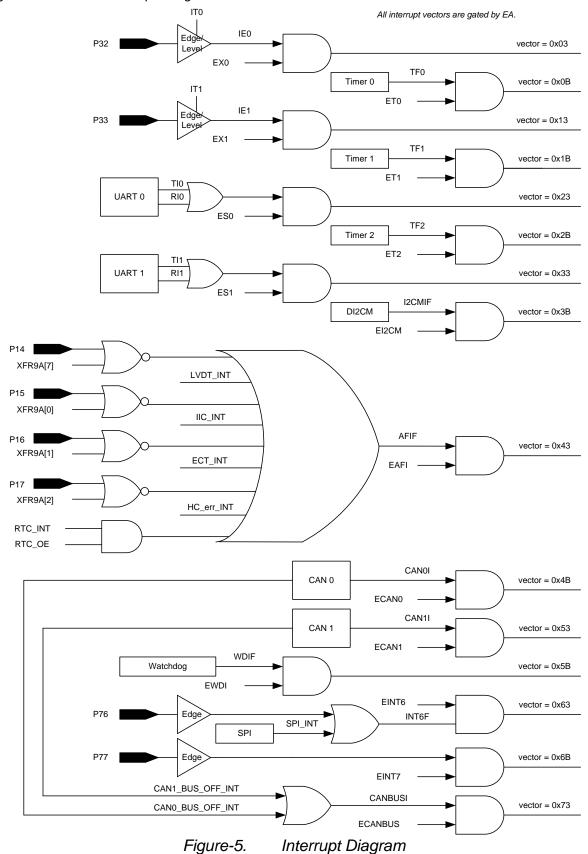

| Figure-5.  | Interrupt Diagram                                                          |     |

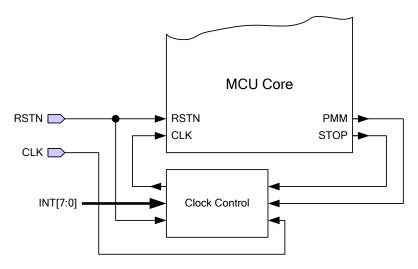

| Figure-6.  | Power Saving Unit Interconnection                                          |     |

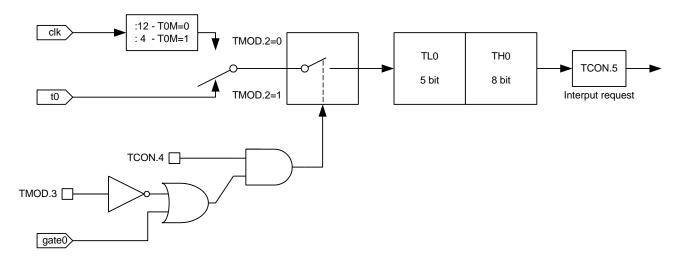

| Figure-7.  | Timer0 Mode 0                                                              |     |

| Figure-8.  | Timer0 Mode 1                                                              | 42  |

| Figure-9.  | Timer0 Mode 2                                                              |     |

| Figure-10. | Timer0 Mode 3                                                              | _   |

| Figure-11. | Timer1 Mode 0                                                              |     |

| Figure-12. | Timer1 Mode1                                                               | 44  |

| Figure-13. | Timer1 Mode1                                                               |     |

| Figure-14. | Timer 2 Capture Mode                                                       |     |

| Figure-15. | Timer 2 Auto-reloaded Mode (DCEN =0)                                       |     |

| Figure-16. | Timer 2 Auto-Reloaded Mode (DCEN =1)                                       |     |

| Figure-17. | Timer 2 As A Baud Rate Generator Mode                                      |     |

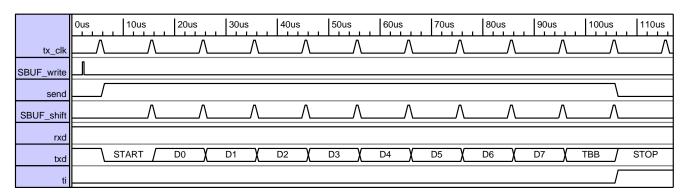

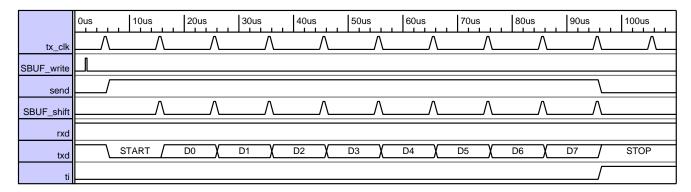

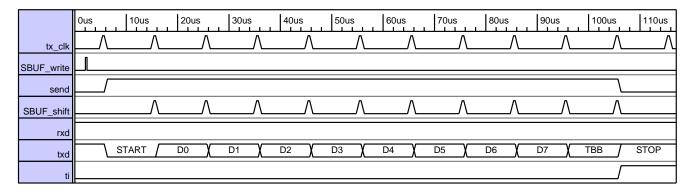

| Figure-18. | UART0 Transmission Mode 0 Timing Diagram                                   | 52  |

| Figure-19. | UART0 Transmission Mode 1 Timing Diagram                                   |     |

| Figure-20. | UART0 Transmission Mode 2 Timing Diagram                                   |     |

| Figure-21. | UART0 Transmission Mode 2 Timing Diagram                                   |     |

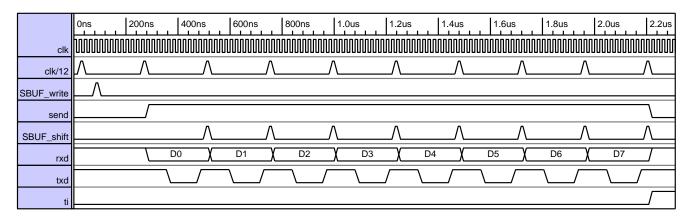

| Figure-22. | UART1 Transmission Mode 0 Timing Diagram                                   |     |

| Figure-23. | UART1 Transmission Mode 1 Timing Diagram                                   |     |

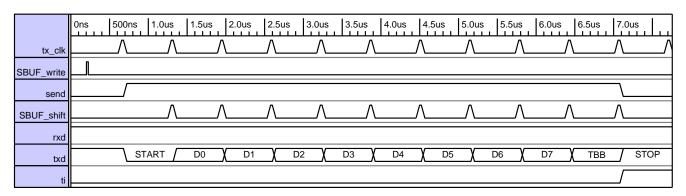

| Figure-24. | UART1 Transmission Mode 2 Timing Diagram                                   |     |

| Figure-25. | UART1 Transmission Mode 3 Timing Diagram                                   |     |

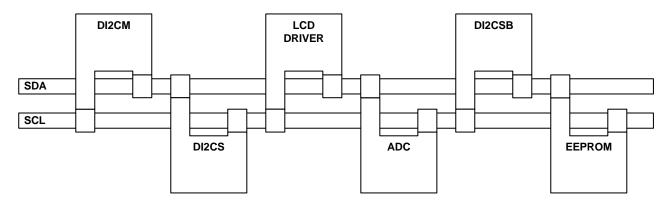

| Figure-26. | An example of I2C-bus application                                          |     |

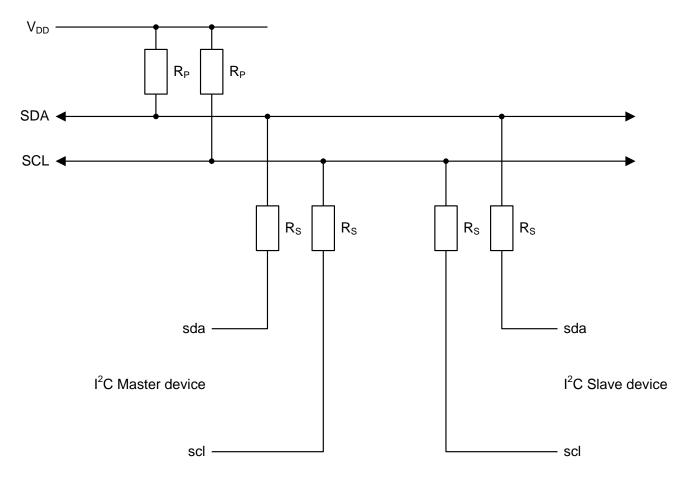

| Figure-27. | Connection Master And Slave Devices To I2c-Bus                             |     |

| Figure-28. | Data Validity During Bit Transfer On The I2C-Bus                           |     |

| Figure-29. | START And STOP Conditions                                                  |     |

| Figure-30. | A Complete Data Transfer With 7-Bit Address                                |     |

| Figure-31. | The First Byte After The START Condition                                   |     |

| Figure-32. | Single SEND Flowchart                                                      |     |

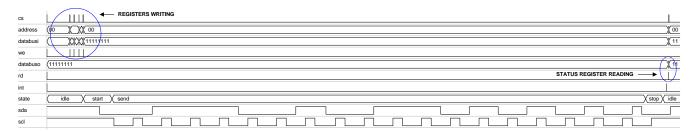

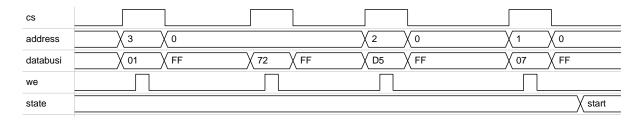

| Figure-33. | Single SEND Waveform                                                       | 71  |

| Figure-34. | Single SEND Waveform - REGISTERS WRITING                                   | 71  |

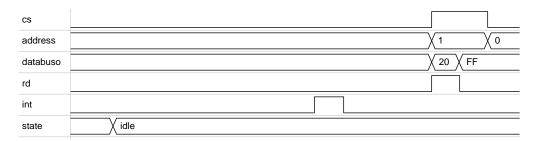

| Figure-35. | Single SEND Waveform - STATUS REGISTER READING                             |     |

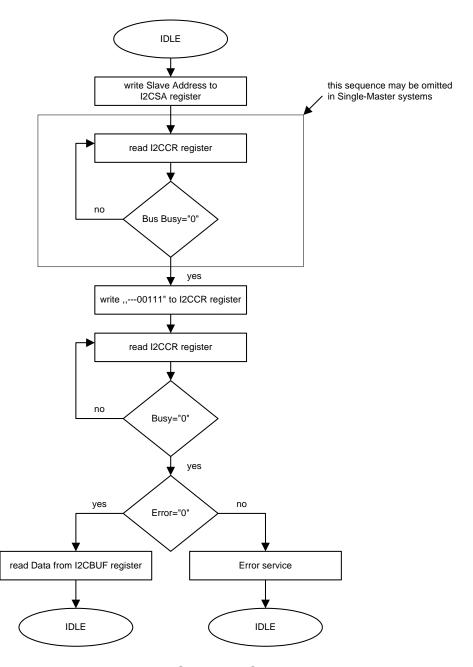

| Figure-36. | Single RECEIVER Flowchart                                                  |     |

| Figure-37. | Single RECEIVE Waveform                                                    |     |

| Figure-38. | Sending n Bytes Flowchart                                                  | 73  |

| Figure-39. | Sending n=3 Bytes Waveform                                                 |     |

| Figure-40. | Receiving m Bytes Flowchart                                                |     |

| Figure-41. | Receiving m=3 Bytes Waveform                                               |     |

| Figure-42. | Sending n Bytes Followed By Repeated Start And Receiving m Bytes Flowchart |     |

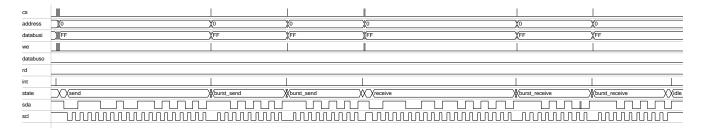

| Figure-43. | Sending 3 Bytes Followed By Repeated Start And Receiving 3 Bytes Waveform  |     |

| Figure-44. | Receiving m Bytes Followed By Repeated Start And Sending n Bytes Flowchart |     |

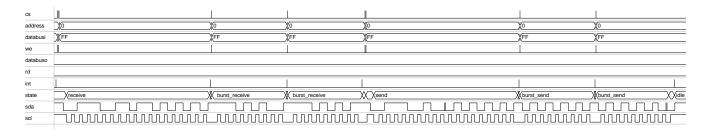

| Figure-45. | Receiving 3 Bytes Followed By Repeated Start And Sending 3 Bytes Waveform  |     |

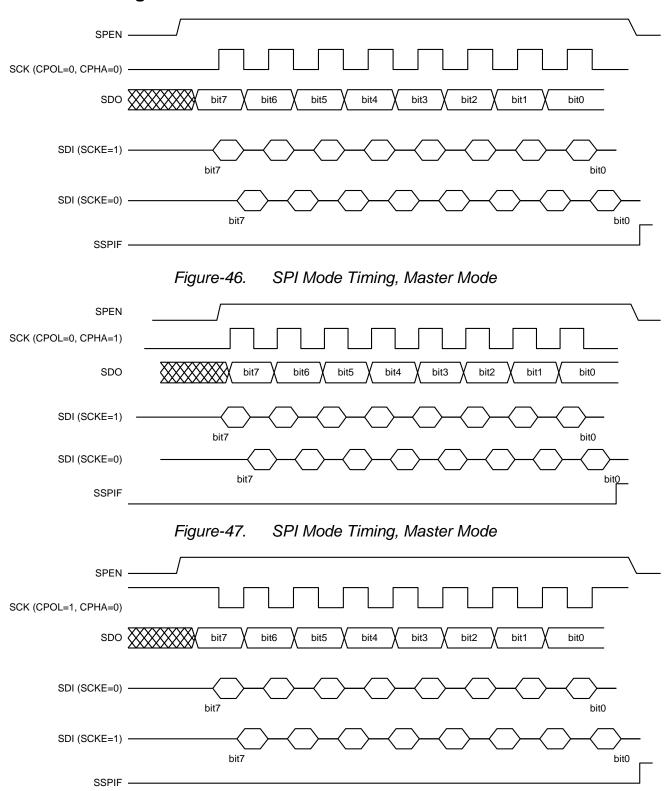

| Figure-46. | SPI Mode Timing, Master Mode                                               |     |

| Figure-47. | SPI Mode Timing, Master Mode                                               |     |

| Figure-48. | SPI Mode Timing, Master Mode                                               |     |

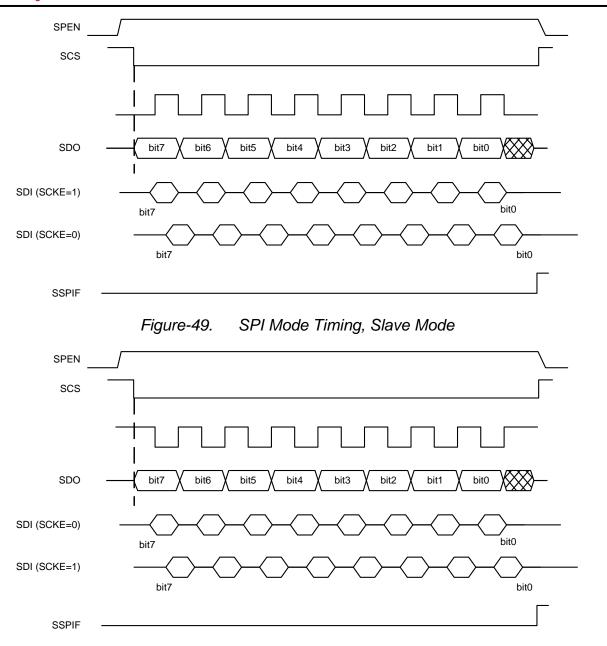

| Figure-49. | SPI Mode Timing, Slave Mode                                                |     |

| Figure-50. | SPI Mode Timing, Slave Mode                                                |     |

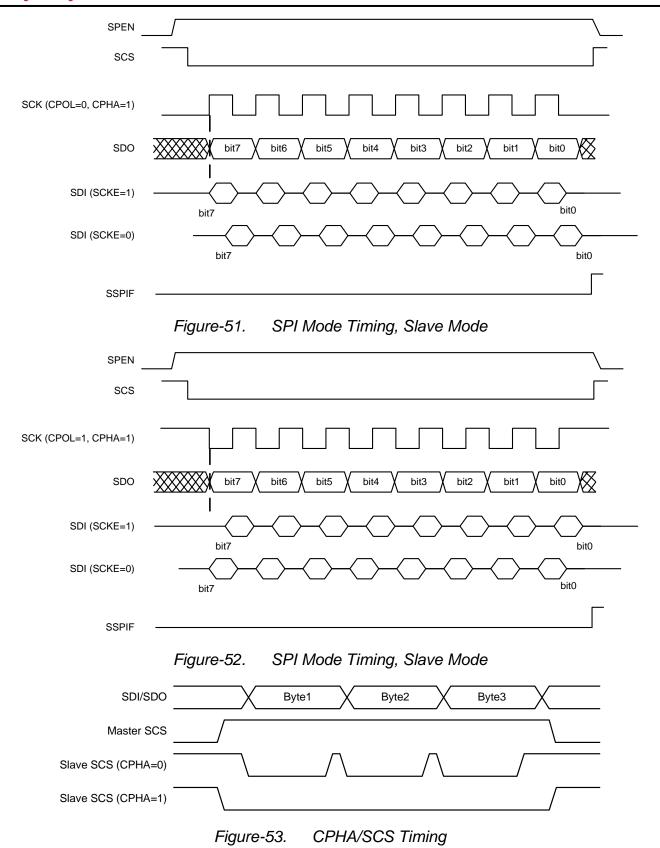

| Figure-51. | SPI Mode Timing, Slave Mode                                                |     |

| Figure-52. | SPI Mode Timing, Slave Mode                                                |     |

| Figure-53. | CPHA/SCS Timing                                                            |     |

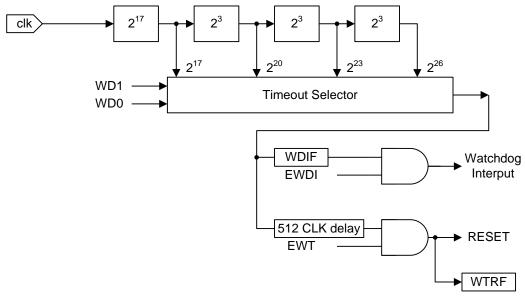

| Figure-54. | Watchdog Timer Structure                                                   |     |

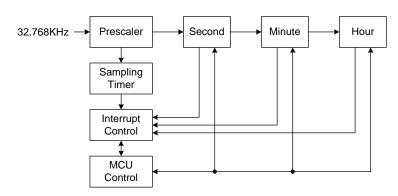

| Figure-55. | RTC Configuration                                                          |     |

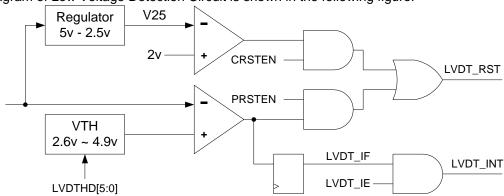

| Figure-56. | LVDT Diagram                                                               | 102 |

# CS8959 PRELIMINARY

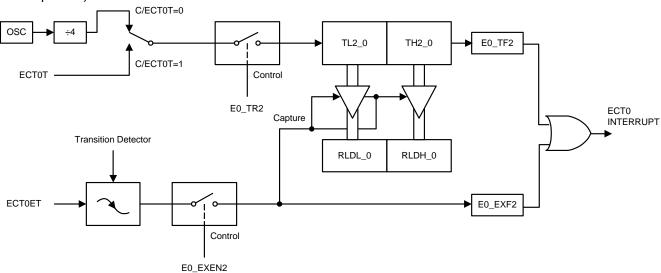

| Figure-57. | ECT0 Capture Mode                                                            | 104 |

|------------|------------------------------------------------------------------------------|-----|

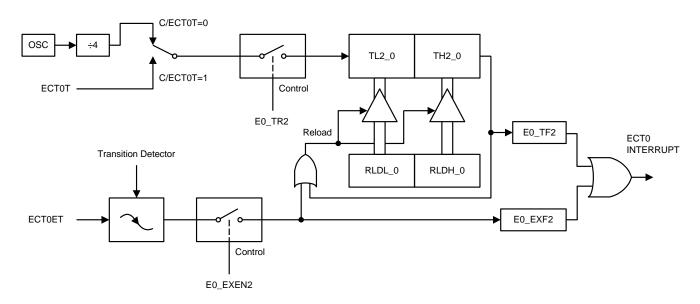

| Figure-58. | ECT0 Auto-Reloaded Mode                                                      | 105 |

| Figure-59. | ECT1 Capture Mode                                                            |     |

| Figure-60. | ECT1 Auto-Reloaded Mode                                                      | 108 |

| Figure-61. | ECT2 Capture Mode                                                            | 110 |

| Figure-62. | ECT2 Auto-Reloaded Mode                                                      | 111 |

| Figure-63. | ECT3 Capture Mode                                                            | 113 |

| Figure-64. | ECT3 Auto-Reloaded Mode                                                      | 114 |

| Figure-65. | ECT4 Capture Mode                                                            | 116 |

| Figure-66. | ECT4 Auto-Reloaded Mode                                                      | 117 |

| Figure-67. | ECT5 Capture Mode                                                            | 119 |

| Figure-68. | ECT5 Auto-Reloaded Mode                                                      | 120 |

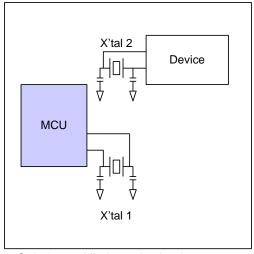

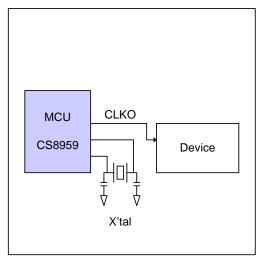

| Figure-69. | CLKO Configuration                                                           | 121 |

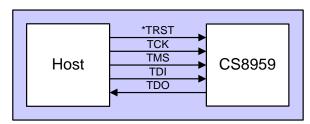

| Figure-70. | Connection via the JTAG interface                                            | 122 |

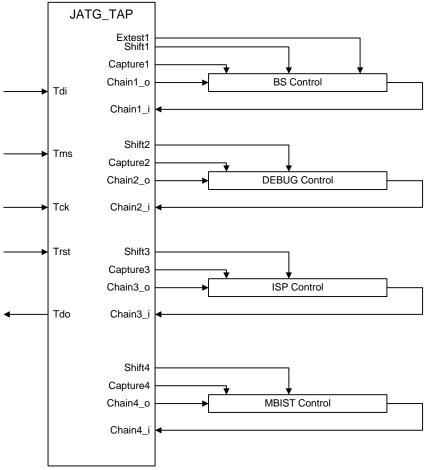

| Figure-71. | Diagram of the JTAG architecture                                             | 122 |

| Figure-72. | General Structure Of A Bit Period                                            | 139 |

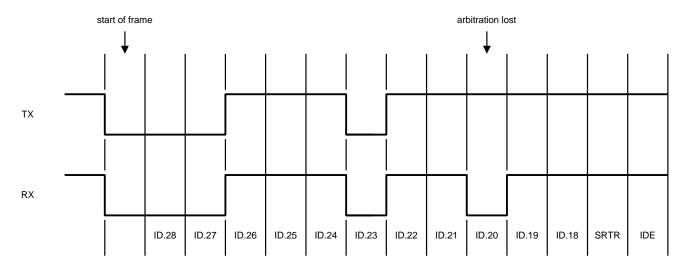

| Figure-73. | Arbitration Lost Bit Number Interpretation                                   | 143 |

| Figure-74. | Example 0f arbitration Lost Bit number Interpretation; Result: ALC = 08H     | 143 |

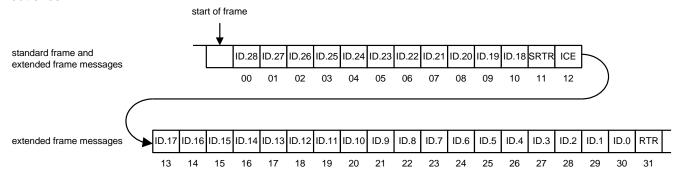

| Figure-75. | Transmit Buffer Layout For Standard And Extended Frame Format Configurations | 148 |

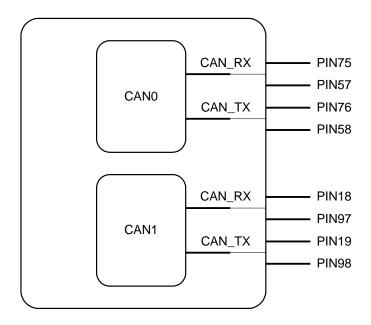

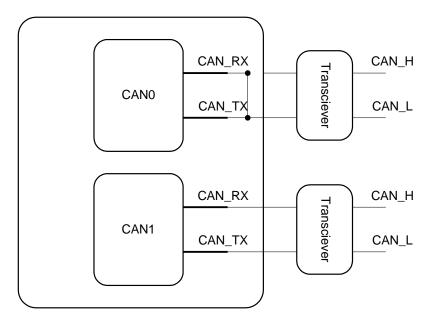

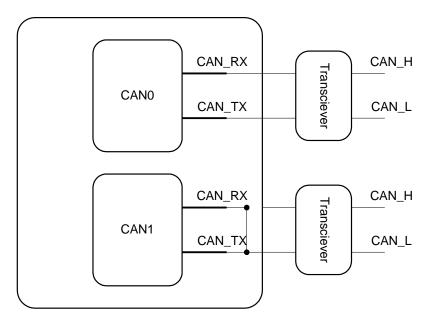

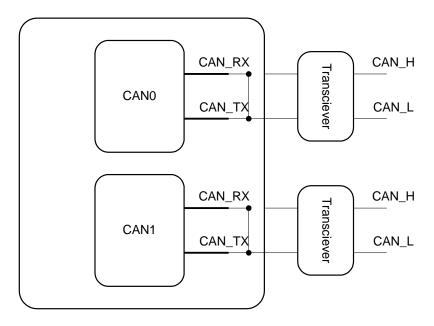

| Figure-76. | CAN TX pin and RX pin distribution                                           | 155 |

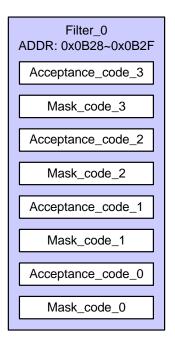

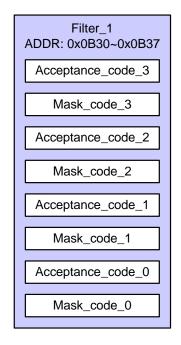

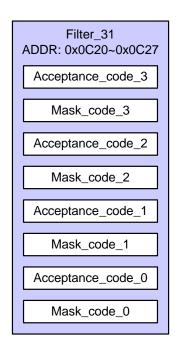

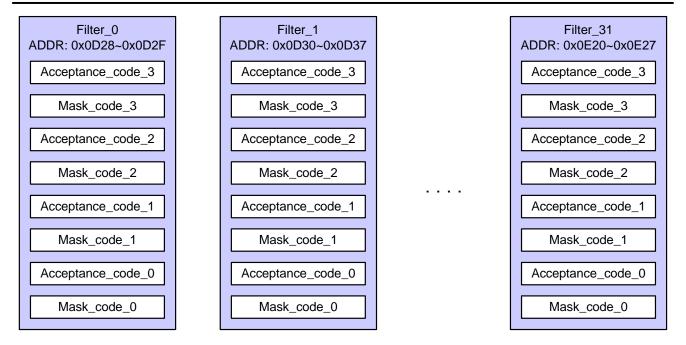

| Figure-77. | CANO Acceptance Filters                                                      | 157 |

| Figure-78. | CAN1 Acceptance Filters                                                      | 158 |

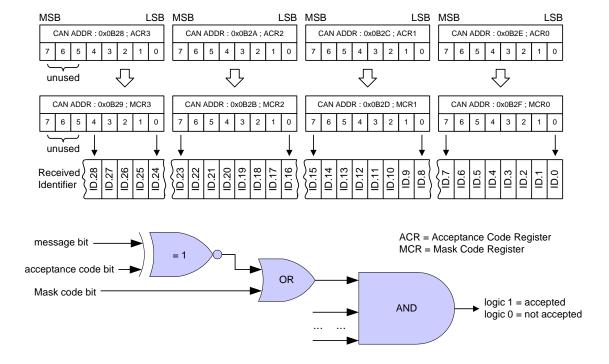

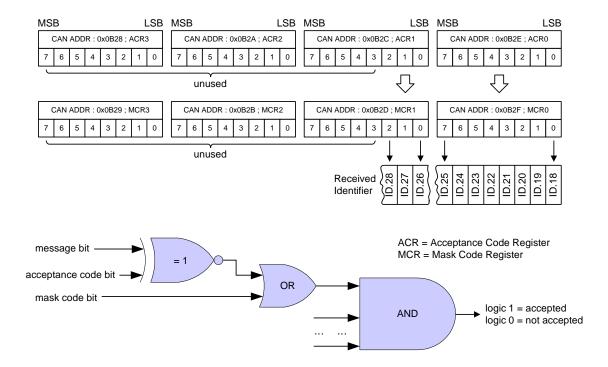

| Figure-79. | Filter 0 In CAN0 Is Receiving Extended Frame Messages                        | 158 |

| Figure-80. | Filter 0 in CAN0 Is Receiving Standard Frame Messages                        | 159 |

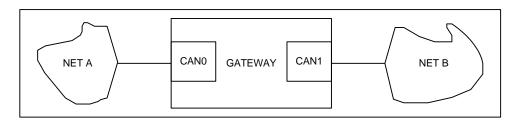

| Figure-81. | Different Nets Connected By CAN Gateway In CS8959                            |     |

| Figure-82. | CAN0 In Self-Loop Test                                                       |     |

| Figure-83. | CAN1 In Self-loop Test                                                       | 163 |

| Figure-84  | Dual Loop Test                                                               | 163 |

# Advanced 8-bit Micro-controller with 171K Flash ROM and Dual CAN controllers

#### 1. GENERAL DESCRIPTION

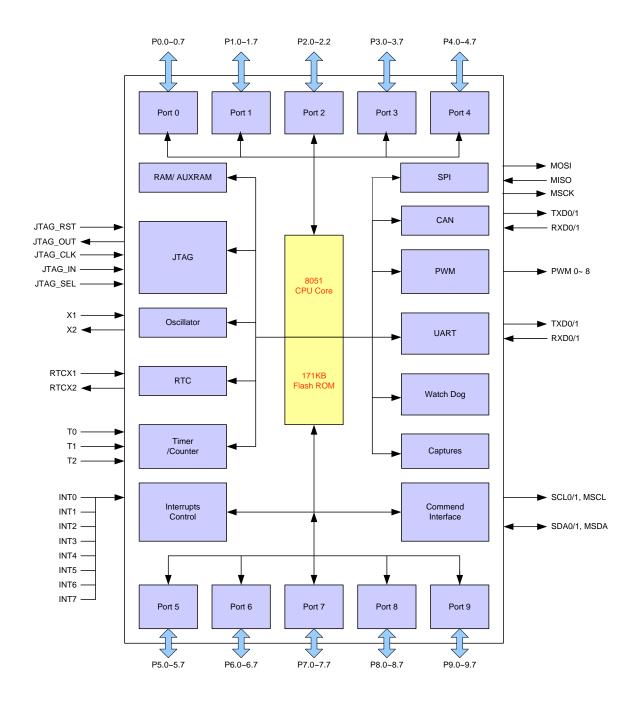

The CS8959 micro-controller is a single-cycle 8051 CPU core embedded device. It includes a 171K-byte internal program Flash ROM, a 256-byte internal RAM, and a 4K-byte auxiliary RAM. It also includes some advanced peripherals such as 2-channels CAN ports, 9 channels of general PWM output ports as well as a Real Time Clock (RTC) module. The Boot-Code-Free ISP (In System Programming) feature allows users to update the programming codes easily via JTAG ports or a UART port. In addition, user can debug system at real time via JTAG interface.

#### 2. FEATURES

- Single Cycle 8051 CPU core, maximum operating clock up to 20 MHz

- Single + 5V (CS8959) power supply

- Embedded 171K-byte Flash ROM with ECC

- 4352-byte RAM with ECC

- 256-byte Internal RAM

- 4K-byte Auxiliary RAM

- 9 channels general PWM outputs

- 7 channel of 8-bit supporting Programmable PWM output frequency

- 2 channel of 8-bit supporting

Programmable PWM output frequency with 4-bits flexible time base period

- Maximum 75 I/O pins

- ECC generation with 1-bit correction

- Three 16-bit Counters/Timers

- One programmable buffered clock output ports to drive peripheral devices

- Built-in one Master and two Slave I<sup>2</sup>C ports

- Built-in SPI controller

- Hardware ISP (In-System-Programming), no Boot Code required

- Two Full-duplex UARTS

- Two CAN controllers with gateway function.

Specification Version 2.0 Part A and B, each one CAN controller provides

- Bit rate up to 1Mbit/s

- 32 Message Objects

- Each Message Object has its own Identifier Mask

- 256 Bytes FIFO

- Interrupt can be masked

- Dispatching registers

- Multi interrupt sources

- Programmable Watch Dog Timer

- Built-in Real Time Clock (RTC)

- Dual Data Pointer (DPTR)

- Flash-ROM program code protection

- JTAG interface Debug System

- Single +5V supply voltage

- Industrial operating temperature range (-40° C ~ +85° C)

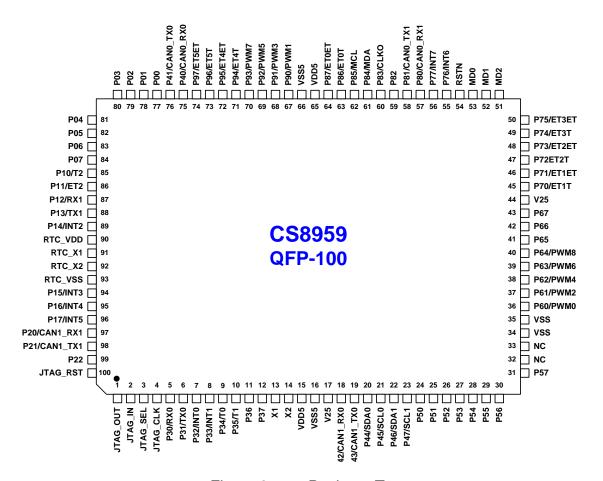

- 100-pin QFP package with RoHs compliance

# Advanced 8-bit Micro-controller with 171K Flash ROM and Dual CAN controllers

# 3. BLOCK DIAGRAM

Figure-1. Block Diagram

### 4. PIN CONNECTION

#### **PACKAGE TYPE**

Figure-2. Package Type

#### 5. PIN DESCRIPTION

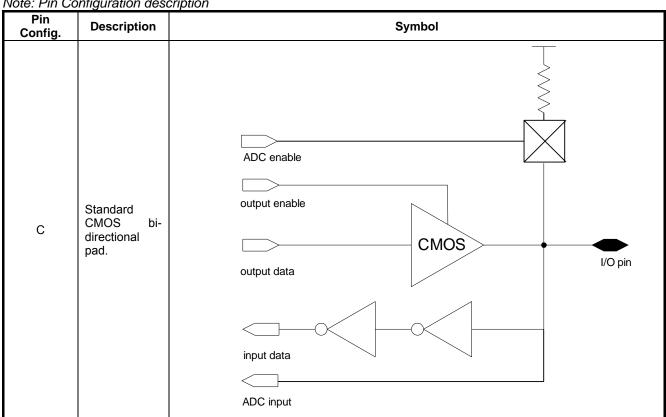

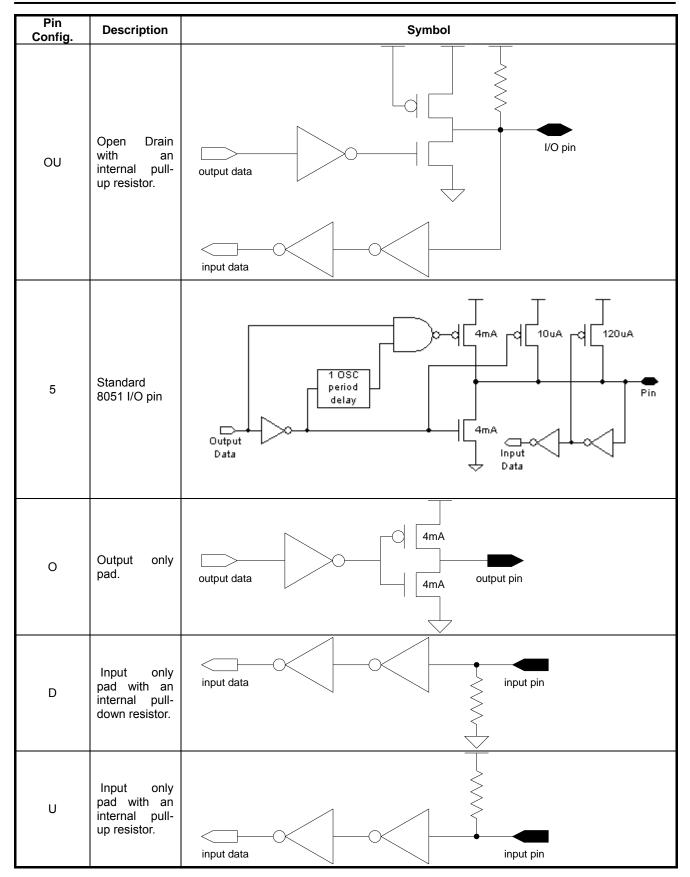

A "CMOS pin" can be used as Input or Output mode. To use these pins as output mode, S/W needs to set the corresponding output enable control bit "Pxxoe" to 1. Otherwise, the "Pxxoe" should clear to 0. In output mode, these pins can sink and drive at least 4mA current.

An "open drain pin" means it can sink at least 4mA current but no drive current to VDD. It can be used as input or output function and need an external pull up resistor.

An "8051 standard pin" is a pseudo open drain pin. It can sink at least 4mA current when output low level, and drive at least 4mA current for 160nS when output transit from low to high, then keep drive 100uA to maintain the pin at high level. It can be used as input or output function. It need an external pull up resistor when drive heavy load device.

The pins functionality is described in the following table. All pins are one directional. There are no three states outputs pins and internal signals.

|                | Pin No.               | . Pin Type   |     | Default  | Pin                                                    |                                                          |  |  |

|----------------|-----------------------|--------------|-----|----------|--------------------------------------------------------|----------------------------------------------------------|--|--|

| Name           | QFP                   | Type Default |     | Function | Configuration                                          | Function Description                                     |  |  |

| JTAG_OUT       | 1                     | 0            | 0   | JTAG_OUT | 0                                                      | JTAG output                                              |  |  |

| JTAG_IN        | 2                     | I            | 1   | JTAG_IN  | U                                                      | JTAG input                                               |  |  |

| JTAG_SEL       | 3                     | Ţ            | 1   | JTAG_SEL | U                                                      | JTAG mode select                                         |  |  |

| JTAG_CLK       | 4                     | I            | I   | JTAG_CLK | D                                                      | JTAG clock input                                         |  |  |

| P30/RX0        | 5                     | I/O          | I   | P30      | 5                                                      | General purpose I/O / UART0 serial receiver input        |  |  |

| P31/TX0        | 6                     | I/O          | 1   | P31      | 5                                                      | General purpose I/O / UART0 serial transmitter output    |  |  |

| P32/INT0/GATE0 | 7                     | I/O          | I   | P32      | 5                                                      | General purpose I/O / External interrupt 0 / Timer0 Gate |  |  |

| P33/INT1/GATE1 | 8                     | I/O          | I   | P33      | 5                                                      | General purpose I/O / External interrupt 1 / Timer1 Gate |  |  |

| P34/T0         | 9                     | I/O          | 1   | P34      | 5                                                      | General purpose I/O / Timer 0 input                      |  |  |

| P35/T1         | 10                    | I/O          | 1   | P35      | 5                                                      | General purpose I/O / Timer 1 input                      |  |  |

| P36            | 11                    | I/O          | 1   | P36      | 5                                                      | General purpose I/O                                      |  |  |

| P37            | 12                    | I/O          | 1   | P37      | 5                                                      | General purpose I/O                                      |  |  |

| X1             | 13                    | I            | I   | X1       | -                                                      | Oscillator input                                         |  |  |

| X2             | 14                    | 0            | 0   | X2       | -                                                      | Oscillator output                                        |  |  |

| VDD5           | 15                    | -            | -   | VDD5     | -                                                      | +5V Positive Power Supply                                |  |  |

| VSS5           | 16                    | -            | -   | VSS5     | -                                                      | Ground                                                   |  |  |

| V25            | 17                    | -            | -   | V25      | -                                                      | +2.5V Positive Power Output                              |  |  |

| P42/CAN_RX1    | 18                    | I/O          | I   | P42      | OU                                                     | General purpose I/O / CAN1 serial transmitter output     |  |  |

| P43/CAN_TX1    | 19                    | I/O          | I   | P43      | OU                                                     | General purpose I/O / CAN1 serial receiver input         |  |  |

| P44/SDA0       | 20 I/O I P44          |              | P44 | OU       | General purpose I/O / Slave IIC 0 bus serial data line |                                                          |  |  |

| P45/SCL0       | P45/SCL0 21 I/O I P45 |              | P45 | OU       | General purpose I/O / Slave IIC 0 bus clock line       |                                                          |  |  |

| P46/SDA1       | 22                    | I/O          | I   | P46      | OU                                                     | General purpose I/O / Slave IIC 1 bus serial data line   |  |  |

| Nama           | Pin No. | n No. Pin Type |         | Default  | Pin           | Function Decembring                                                           |  |  |

|----------------|---------|----------------|---------|----------|---------------|-------------------------------------------------------------------------------|--|--|

| Name           | QFP     | Туре           | Default | Function | Configuration | Function Description                                                          |  |  |

| P47/SCL1       | 23      | I/O            | I       | P47      | OU            | General purpose I/O / Slave IIC 1 bus clock line                              |  |  |

| P50            | 24      | I/O            | I       | P50      | С             | General purpose I/O                                                           |  |  |

| P51            | 25      | I/O            | 1       | P51      | С             | General purpose I/O                                                           |  |  |

| P52            | 26      | I/O            | 1       | P52      | С             | General purpose I/O                                                           |  |  |

| P53            | 27      | I/O            | 1       | P53      | С             | General purpose I/O                                                           |  |  |

| P54            | 28      | I/O            | 1       | P54      | С             | General purpose I/O                                                           |  |  |

| P55            | 29      | I/O            | 1       | P55      | С             | General purpose I/O                                                           |  |  |

| P56            | 30      | I/O            | 1       | P56      | С             | General purpose I/O                                                           |  |  |

| P57            | 31      | I/O            | 1       | P57      | С             | General purpose I/O                                                           |  |  |

| NC             | 32      | -              | -       | NC       | -             | NC                                                                            |  |  |

| NC             | 33      | -              | -       | NC       | -             | NC                                                                            |  |  |

| VSS            | 34      | -              | -       | VSS      | -             | Ground                                                                        |  |  |

| VSS            | 35      | -              | -       | VSS      | -             | Ground                                                                        |  |  |

| P60/PWM0       | 36      | I/O            | I       | P60      | OU            | General purpose I/O / 8-bit PWM DAC output (with 4-BIT prescaler)             |  |  |

| P61/PWM2       | 37      | I/O            | I       | P61      | OU            | General purpose I/O / 8-bit PWM DAC output                                    |  |  |

| P62/PWM4       | 38      | I/O            | I       | P62      | OU            | General purpose I/O / 8-bit PWM DAC output                                    |  |  |

| P63/PWM6       | 39      | I/O            | I       | P63      | OU            | General purpose I/O / 8-bit PWM DAC output                                    |  |  |

| P64/PWM8       | 40      | I/O            | I       | P64      | OU            | General purpose I/O / 8-bit PWM DAC output                                    |  |  |

| P65            | 41      | I/O            | 1       | P65      | С             | General purpose I/O                                                           |  |  |

| P66            | 42      | I/O            | 1       | P66      | С             | General purpose I/O                                                           |  |  |

| P67            | 43      | I/O            | I       | P67      | С             | General purpose I/O                                                           |  |  |

| V25            | 44      | -              | -       | V25      | -             | +2.5V Positive Power Output                                                   |  |  |

| P70/ET1T       | 45      | I/O            | 1       | P70      | 5             | General purpose I/O / ECT1 Input.                                             |  |  |

| P71/ET1ET      | 46      | I/O            | 1       | P71      | 5             | General purpose I/O / ECT1 trigger Input.                                     |  |  |

| P72/ET2T/SCS   | 47      | I/O            | I       | P72      | 5             | General purpose I/O / ECT2 Input / SPI chip select.                           |  |  |

| P73/ET2ET/MOSI | 48      | I/O            | I       | P73      | 5             | General purpose I/O / ECT2 trigger Input / SPI Master output and Slave input. |  |  |

| P74/ET3T/MISO  | 49      | I/O            | I       | P74      | 5             | General purpose I/O / ECT3 Input / SPI Master input and Slave output.         |  |  |

| P75/ET3ET/MSCK | 50      | I/O            | ı       | P75      | 5             | General purpose I/O / ECT3 trigger Input / SPI Master clock output.           |  |  |

| MD2            | 51      | I              | I       | MD2      | D             | Work mode select, shall connect to VSS25                                      |  |  |

| MD1            | 52      | I              | I       | MD1      | D             | Work mode select, shall connect to VSS25                                      |  |  |

| MD0            | 53      | I              | I       | MDO      | D             | Work mode select, shall connect to VSS25                                      |  |  |

|             | Pin No. | . Pin Type |         | Default  | Pin           |                                                                   |  |  |

|-------------|---------|------------|---------|----------|---------------|-------------------------------------------------------------------|--|--|

| Name        | QFP     | Туре       | Default | Function | Configuration | Function Description                                              |  |  |

| RSTN        | 54      | 1          | I       | RSTN     | U             | Active low reset.                                                 |  |  |

| P76/INT6    | 55      | I/O        | I       | P76      | 5             | General purpose I/O / External interrupt 6.                       |  |  |

| P77/INT7    | 56      | I/O        | 1       | P77      | 5             | General purpose I/O / External interrupt 7                        |  |  |

| P80/CAN_RX0 | 57      | I/O        | 1       | P80      | OU            | General purpose I/O / CAN0 serial receiver input.                 |  |  |

| P81/CAN_TX0 | 58      | I/O        | I       | P81      | OU            | General purpose I/O / CAN0 serial transmitter output.             |  |  |

| P82         | 59      | I/O        | 1       | P82      | 5             | General purpose I/O                                               |  |  |

| P83/CLKO    | 60      | I/O        | I       | P83      | 5             | General purpose I/O / Oscillator Frequency Clock output           |  |  |

| P84/MDA     | 61      | I/O        | I       | P84      | OU            | General purpose I/O / Master IIC bus serial data line.            |  |  |

| P85/MCL     | 62      | I/O        | I       | P85      | OU            | General purpose I/O / Master IIC bus clock line                   |  |  |

| P86/ET0T    | 63      | I/O        | I       | P86      | 5             | General purpose I/O / ECT0 Input.                                 |  |  |

| P87/ET0ET   | 64      | I/O        | I       | P87      | 5             | General purpose I/O / ECT0 trigger Input.                         |  |  |

| VDD5        | 65      | -          | -       | VDD5     | -             | +5V Positive Power Supply                                         |  |  |

| VSS5        | 66      | -          | -       | VSS5     | -             | Ground                                                            |  |  |

| P90/PWM1    | 67      | I/O        | I       | P90      | OU            | General purpose I/O / 8-bit PWM DAC output (with 4-BIT prescaler) |  |  |

| P91/PWM3    | 68      | I/O        | I       | P91      | OU            | General purpose I/O / 8-bit PWM DAC output                        |  |  |

| P92/PWM5    | 69      | I/O        | 1       | P92      | OU            | General purpose I/O / 8-bit PWM DAC output                        |  |  |

| P93/PWM7    | 70      | I/O        | I       | P93      | OU            | General purpose I/O / 8-bit PWM DAC output                        |  |  |

| P94/ET4T    | 71      | I/O        | 1       | P94      | 5             | General purpose I/O / ECT4 Input.                                 |  |  |

| P95/ET4ET   | 72      | I/O        | 1       | P95      | 5             | General purpose I/O / ECT4 trigger Input.                         |  |  |

| P96/ET5T    | 73      | I/O        | I       | P96      | 5             | General purpose I/O / ECT5 Input.                                 |  |  |

| P97/ET5ET   | 74      | I/O        | 1       | P97      | 5             | General purpose I/O / ECT5 trigger Input.                         |  |  |

| P40/CAN_RX0 | 75      | I/O        | 1       | P40      | OU            | General purpose I/O / CAN0 serial receiver input.                 |  |  |

| P41/CAN_TX0 | 76      | I/O        | 1       | P41      | OU            | General purpose I/O / CAN0 serial transmitter output.             |  |  |

| P00         | 77      | I/O        | I       | P00      | 5             | General purpose I/O                                               |  |  |

| P01         | 78      | I/O        | I       | P01      | 5             | General purpose I/O                                               |  |  |

| P02         | 79      | I/O        | I       | P02      | 5             | General purpose I/O                                               |  |  |

| P03         | 80      | I/O        | I       | P03      | 5             | General purpose I/O                                               |  |  |

| P04         | 81      | I/O        | 1       | P04      | 5             | General purpose I/O                                               |  |  |

| P05         | 82      | I/O        | 1       | P05      | 5             | General purpose I/O                                               |  |  |

| P06         | 83      | I/O        | I       | P06      | 5             | General purpose I/O                                               |  |  |

| P07         | 84      | I/O        | I       | P07      | 5             | General purpose I/O                                               |  |  |

| P10/T2      | 85      | I/O        | I       | P10      | 5             | General purpose I/O / External Timer 2 Input;                     |  |  |

| P11/T2EX    | 86      | I/O        | I       | P11      | 5             | General purpose I/O / External Timer 2 trigger Input              |  |  |

| Nama        | Pin No. Pin T |      | Гуре    | Default  | Pin           | Formation Bookington                                  |  |  |

|-------------|---------------|------|---------|----------|---------------|-------------------------------------------------------|--|--|

| Name        | QFP           | Туре | Default | Function | Configuration | Function Description                                  |  |  |

| P12/RX1     | 87            | I/O  | 1       | P12      | 5             | General purpose I/O / UART1 serial receiver input     |  |  |

| P13/TX1     | 88            | I/O  | I       | P13      | 5             | General purpose I/O / UART1 serial transmitter output |  |  |

| P14/INT2    | 89            | I/O  | 1       | P14      | 5             | General purpose I/O / External interrupt 2            |  |  |

| RTC_VDD     | 90            | -    | -       | RTC_VDD  | -             | RTC Power Supply                                      |  |  |

| RTC_X1      | 91            | 1    | Ι       | RTC_X1   | -             | RTC clock input                                       |  |  |

| RTC_X2      | 92            | 0    | 0       | RTC_X2   | -             | RTC clock output                                      |  |  |

| RTC_VSS     | 93            | -    | -       | RTC_VSS  | -             | RTC ground                                            |  |  |

| P15/INT3    | 94            | I/O  |         | P15      | С             | General purpose I/O / External interrupt 3            |  |  |

| P16/INT4    | 95            | I/O  | 1       | P16      | С             | General purpose I/O / External interrupt 4            |  |  |

| P17/INT5    | 96            | I/O  | Ι       | P17      | С             | General purpose I/O / External interrupt 5            |  |  |

| P20/CAN_RX1 | 97            | I/O  | 1       | P20      | OU            | General purpose I/O / CAN1 serial receiver input.     |  |  |

| P21/CAN_TX1 | 98            | I/O  | I       | P21      | OU            | General purpose I/O / CAN1 serial transmitter output. |  |  |

| P22         | 99            | I/O  | 1       | P22      | 5             | General purpose I/O                                   |  |  |

| JTAG_RST    | 100           | I    | 1       | JTAG_RST | D             | Reset JTAG module, active high reset                  |  |  |

Note: Pin Configuration description

#### 6. MEMORY ALLOCATION

# 6.1 INTERNAL SPECIAL FUNCTION REGISTERS (SFR)

The SFR is a group of registers that are the same as standard 8051.

#### 6.2 INTERNAL RAM

There are total 256 bytes internal RAM in CS8959, the same as standard 8052.

# 6.3 EXTERNAL SPECIAL FUNCTION REGISTERS (XFR)

The XFR is a group of registers allocated in the 8051 external RAM area 0X0F00 - 0X0FFF. These registers are used for special functions. Programs can use "MOVX" instruction to access these registers.

#### 6.4 CAN REGISTERS

There are total 1024 bytes CAN Registers allocated in the 8051 external RAM area 0X0B00 – 0X0EFF. Programs can use "MOVX" instruction to access the CAN Registers

### 6.5 AUXILIARY RAM (AUXRAM)

There are total 4K auxiliary RAM allocated in the 8051 external RAM area 0X1000h – 0X1FFF. Programs can use "MOVX" instruction to access the AUXRAM.

| 0XFF         | Internal RAM Accessible by indirect addressing only (Using          | SFR  Accessible by direct addressing | 0X1FFF<br>0X1000 | 4KB AUXRAM Accessible by indirect external RAM addressing (Using MOVX instruction) |

|--------------|---------------------------------------------------------------------|--------------------------------------|------------------|------------------------------------------------------------------------------------|

| 0X80<br>0X7F | MOV A,@Ri<br>instruction)  Internal RAM Accessible by<br>direct and |                                      | 0X0FFF<br>0X0F00 | XFR Accessible by indirect external RAM addressing (Using MOVX instruction)        |

| 0X00         | indirect<br>addressing                                              |                                      | 0X0EFF           | CAN Accessible by indirect external RAM addressing (Using MOVX instruction)        |

|              |                                                                     |                                      | 0X0B00           | (Using MOVA Instruction)                                                           |

Figure-3. Auxiliary RAM

# 7. MEMORY MAP OF XFR (0X0F00---0X0FFF)

| Reg. name | address      | bit7                      | bit6                                  | bit5      | bit4         | bit3         | bit2    | bit1   | bit0    |  |

|-----------|--------------|---------------------------|---------------------------------------|-----------|--------------|--------------|---------|--------|---------|--|

| IICSTUS0  | 0X0F01 (r)   | WadrB0                    |                                       | SlvRWB0   | SackIn0      | SLVS0        |         |        |         |  |

| INTFLG0   | 0X0F03 (r)   | TXBI0                     | RCBI0                                 | SIvBMI0   | STOPI0       | ReStal0      |         |        |         |  |

| INTFLG0   | 0X0F03 (w)   |                           |                                       | SIvBMI0   | STOPI0       | ReStal0      |         |        |         |  |

| INTEN0    | 0X0F04 (w)   | ETXBI0                    | ERCBI0                                | ESIvBMI0  | ESTOPIO      | EreStal0     |         |        |         |  |

| RCBBUF0   | 0X0F08 (r)   |                           |                                       | SI        | ave B 0 IIC  | receives b   | uffer   | •      |         |  |

| TXBBUF0   | 0X0F08 (w)   |                           |                                       | Sla       | ave B 0 IIC  | transmits b  | uffer   |        |         |  |

| SLVBADR0  | 0X0F09 (w)   | ENSIvB0                   |                                       |           | Slav         | e B 0 IIC a  | ddress  |        |         |  |

| ISPSLV    | 0X0F0B (w)   |                           |                                       | ISP Slave | address      |              |         |        |         |  |

| ISPEN     | 0X0F0C (w)   |                           |                                       | Wr        | ite 92h to e | nable ISP I  | Mode    |        |         |  |

| ISPCMP1   | 0X0F0D (w)   |                           |                                       | I         | SP compar    | ed data 1 [7 | 7:0]    |        |         |  |

| ISPCMP2   | 0X0F0E (w)   |                           |                                       | Į:        | SP compar    | ed data 2 [7 | 7:0]    |        |         |  |

| ISPCMP3   | 0X0F0F (w)   |                           |                                       | Į:        | SP compar    | ed data 3 [7 | 7:0]    |        |         |  |

| DA0       | 0X0F20 (r/w) |                           |                                       | Р         | ulse width   | of PWM DA    | C 0     |        |         |  |

| DA1       | 0X0F21 (r/w) |                           | Pulse width of PWM DAC 1              |           |              |              |         |        |         |  |

| DA2       | 0X0F22 (r/w) |                           | Pulse width of PWM DAC 2              |           |              |              |         |        |         |  |

| DA3       | 0X0F23 (r/w) |                           | Pulse width of PWM DAC 3              |           |              |              |         |        |         |  |

| DA4       | 0X0F24 (r/w) |                           | Pulse width of PWM DAC 4              |           |              |              |         |        |         |  |

| DA5       | 0X0F25 (r/w) |                           |                                       | Р         | ulse width   | of PWM DA    | C 5     |        |         |  |

| DA6       | 0X0F26 (r/w) |                           |                                       | Р         | ulse width   | of PWM DA    | C 6     |        |         |  |

| DA7       | 0X0F27 (r/w) |                           |                                       | Р         | ulse width   | of PWM DA    | C 7     |        |         |  |

| DA8       | 0X0F28 (r/w) |                           |                                       | Р         | ulse width   | of PWM DA    | .C 8    |        |         |  |

| RESERVED  | 0X0F29 (r/w) | -                         | -                                     | -         | -            | -            | -       | -      | -       |  |

| RESERVED  | 0X0F2A (r/w) | -                         | -                                     | -         | -            | -            | -       | -      | -       |  |

| PFC       | 0X0F2B (r/w) | PFC13                     | PFC12                                 | PFC11     | PFC10        | PFC03        | PFC02   | PFC01  | PFC00   |  |

| PADMOD0   | 0X0F50 (r/w) | SPI_MOD                   |                                       |           |              |              |         |        | DA8E    |  |

| PADMOD1   | 0X0F51 (r/w) | DA7E                      | DA6E                                  | DA5E      | DA4E         | DA3E         | DA2E    | DA1E   | DA0E    |  |

| PADMOD2   | 0X0F52 (r/w) | HIIC1E                    | MIICEN                                | HIIC0E    | CKOE         | CAN0EN       | CAN0EN1 | CAN1EN | CAN1EN1 |  |

| SEL       | 0X0F55 (w)   |                           | TRTC                                  | WKOSC     | LPS          | CKSL1        | CKSL2   |        |         |  |

| OPTION    | 0X0F56 (w)   | PWMF DIV253 ENSCL1 ENSCL0 |                                       |           |              |              |         |        |         |  |

| IICSTUS1  | 0X0F91 (w)   | WadrB1                    |                                       | SlvRWB1   | Sackin1      | SLVS1        |         |        |         |  |

| INTFLG1   | 0X0F93 (r)   | TXBI1                     | RCBI1                                 | SIvBMI1   | STOPI1       | ReStal1      |         |        |         |  |

| INTFLG1   | 0X0F93 (w)   | SIvBMI1 STOPI1 ReStal1    |                                       |           |              |              |         |        |         |  |

| INTEN1    | 0X0F94 (w)   | ETXBI1                    | ETXBI1 ERCBI1 ESIvBMI1 ESTOP1 Erstal1 |           |              |              |         |        |         |  |

| RCBBUF1   | 0X0F98 (r)   |                           |                                       | S         | aveB 1 IIC   | receives bu  | uffer   | ,      |         |  |

| TXBBUF1   | 0X0F98 (w)   |                           |                                       | SI        | aveB 1 IIC   | transmits b  | uffer   |        |         |  |

# CS8959 PRELIMINARY

| Reg. name | address      | bit7    | bit6                 | bit5 | bit4  | bit3   | bit2    | bit1    | bit0    |

|-----------|--------------|---------|----------------------|------|-------|--------|---------|---------|---------|

| SLVBADR1  | 0X0F99 (w)   | EnslvB1 | SlaveB 1 IIC address |      |       |        |         |         |         |

| EXINTEN   | 0X0F9A (w)   | INT2EN  |                      |      |       |        | INT5EN  | INT4EN  | INT3EN  |

| EXINTFLG  | 0X0F9B (r/w) | INT2FLG |                      |      |       |        | INT5FLG | INT4FLG | INT3FLG |

| ECCINTEN  | 0X0F9C (r/w) | PUSEN   |                      |      | PRGEN | D256EN | D4KEN   | CAN0EN  | CAN1EN  |

| Reg. name | address      | bit7 | bit6                 | bit5       | bit4     | bit3  | bit2   | bit1   | bit0  |

|-----------|--------------|------|----------------------|------------|----------|-------|--------|--------|-------|

| ECCINTFLG | 0X0F9D (r/w) |      | PRGF                 |            |          | D256F | D4KF   | CAN0F  | CAN1F |

| POWER     | 0X0F9E (r/w) | EN   | FLAG                 |            |          |       | PRSTEN | CRSTEN |       |

| PSCON     | 0X0F9F (r/w) | -    | ;                    | SWBSEL[2:0 | )]       | CAHEN |        |        |       |

| RTCCON    | 0X0FE0 (w)   |      | RTC register address |            |          |       |        | -      |       |

| RTCDAT    | 0X0FE1 (r/w) |      |                      |            | ata[7:0] |       |        |        |       |

# 7.1 Chip CONFIGURATION

= 0

The Chip Configuration registers define configuration of the chip and function of the pins.

PADMOD0 (r/w): (XFR 0X0F50) Pad mode control registers 0. (default 0X00)

|         | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|-------|-------|-------|-------|-------|-------|-------|

| Name    | SPI_MOD | -     | -     | -     | -     | -     | -     | DA8E  |

| Default | 0       | -     | -     | -     | -     | -     | -     | 0     |

PADMOD1 (r/w): (XFR 0X0F51) Pad mode control registers 1. (default 0X00)

$\rightarrow$  Pin "P6.4/PWM8" is P6.4.

|         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Name    | DA7E  | DA6E  | DA5E  | DA4E  | DA3E  | DA2E  | DA1E  | DA0E  |  |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| DA7E | = 1 | $\rightarrow$ Pin "P9.3/PWM7" is PWM7. |

|------|-----|----------------------------------------|

|      | = 0 | $\rightarrow$ Pin "P9.3/PWM7" is P9.3. |

| DA6E | = 1 | $\rightarrow$ Pin "P6.3/PWM6" is PWM6. |

|      | = 0 | $\rightarrow$ Pin "P6.3/PWM6" is P6.3. |

| DA5E | = 1 | $\rightarrow$ Pin "P9.2/PWM5" is PWM5. |

|      | = 0 | $\rightarrow$ Pin "P9.2/PWM5" is P9.2. |

| DA4E | = 1 | $\rightarrow$ Pin "P6.2/PWM4" is PWM4. |

|      | = 0 | $\rightarrow$ Pin "P6.2/PWM4" is P6.2. |

| DA3E | = 1 | $\rightarrow$ Pin "P9.1/PWM3" is PWM3. |

|      | = 0 | $\rightarrow$ Pin "P9.1/PWM3" is P9.1. |

| DA2E | = 1 | $\rightarrow$ Pin "P6.1/PWM2" is PWM2. |

|      | = 0 | $\rightarrow$ Pin "P6.1/PWM2" is P6.1. |

| DA1E | = 1 | $\rightarrow$ Pin "P9.0/PWM1" is PWM1. |

|      | = 0 | $\rightarrow$ Pin "P9.0/PWM1" is P9.0. |

| DA0E | = 1 | $\rightarrow$ Pin "P6.0/PWM0" is PWM0. |

|      | = 0 | $\rightarrow$ Pin "P6.0/PWM0" is P6.0. |

|      |     |                                        |

PADMOD2 (r/w): (XFR 0X0F52) Pad mode control registers 2. (default 0X00)

|         | Bit 7  | Bit 6  | Bit 5  | Bit 4 | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|--------|--------|--------|-------|---------|---------|---------|---------|

| Name    | HIIC1E | MIICEN | HIIC0E | CKOE  | CAN0EN0 | CAN0EN1 | CAN1EN0 | CAN1EN1 |

| Default | 0      | 0      | 0      | 0     | 0       | 0       | 0       | 0       |

| HIIC1E  | = 1 | $\rightarrow$ Pin "SCL1/P4.7" is SCL1;        | pin "HSDA1/P4.6" is SDA1.       |

|---------|-----|-----------------------------------------------|---------------------------------|

|         | = 0 | $\rightarrow$ Pin "SCL1/P4.7" is P4.7;        | pin "SDA1/P4.6" is P4.6.        |

| MIICEN  | = 1 | $\rightarrow$ Pin "MCL/P8.5" is MCL;          | pin "MDA/P8.4" is MDA.          |

|         | = 0 | $\rightarrow$ Pin "MCL/P8.5" is P8.5;         | pin "MDA/P8.4" is P8.4.         |

| HIIC0E  | = 1 | $\rightarrow$ Pin "SCL0/P4.5" is SCL0.        | Pin "SDA0/P4.4" is SDA0.        |

|         | = 0 | $\rightarrow$ Pin "SCL0/P4.5" is P4.5.        | Pin "SDA0/P4.4" is P4.4.        |

| CKOE    | = 1 | $\rightarrow$ Pin "P8.3/CLKO" is CLKO.        |                                 |

|         | = 0 | $\rightarrow$ Pin "P8.3/CLKO" is p8.3.        |                                 |

| CAN0EN0 | = 1 | $\rightarrow$ Pin "CAN_RX0/P4.0" is CAN0_RX0; | pin "CAN_TX0/P4.1" is CAN0_TX0. |

|         | = 0 | $\rightarrow$ Pin "CAN_RX0/P4.0" is P4.0;     | pin "CAN_TX0/ P4.1" is P4.1.    |

| CAN0EN1 | = 1 | $\rightarrow$ Pin "CAN_RX0/P8.0" is CAN1_RX0; | pin "CAN_TX0/P8.1" is CAN1_TX0. |

|         | = 0 | $\rightarrow$ Pin "CAN_RX0/P8.0" is P8.0;     | pin "CAN_TX0/ P8.1" is P8.1.    |

| CAN1EN0 | = 1 | $\rightarrow$ Pin "CAN_RX1/P4.2" is CAN1_RX0; | pin "CAN_TX1/P4.3" is CAN1_TX0. |

|         | = 0 | $\rightarrow$ Pin "CAN_RX1/P4.2" is P4.2;     | pin "CAN_TX1/ P4.3" is P4.3.    |

| CAN1EN1 | = 1 | $\rightarrow$ Pin "CAN_RX1/P2.0" is CAN1_RX1; | pin "CAN_TX1/P2.1" is CAN1_TX1. |

|         | = 0 | $\rightarrow$ Pin "CAN_RX1/P2.0" is P2.0;     | pin "CAN_TX1/ P2.1" is P2.1.    |

OPTION (r/w): (XFR 0X0F56) chip option configuration (default 0X00)

|         | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|--------|-------|--------|--------|-------|-------|-------|

| Name    | PWMF  | DIV253 | -     | ENSCL1 | ENSCL0 | -     | -     | -     |

| Default | 0     | 0      | -     | 0      | 0      | -     | -     | -     |

PWMF = 1  $\rightarrow$  Selects system clock/512 as PWM clock frequency.

= 0  $\rightarrow$  Selects system clock/1024 as PWM clock frequency.

DIV253 = 1  $\rightarrow$  PWM pulse width is 253-step resolution.

$= 0 \rightarrow PWM$  pulse width is 256-step resolution.

ENSCL1 = 1  $\rightarrow$  Enable SlaveB 1 IIC block to hold SCL pin low while CS8959 is unable to catch-up

with the external master's speed.

ENSCL0 = 1 → Enable SlaveB 0 IIC block to hold SCL pin low while CS8959 is unable to catch-up

with the external master's speed.

PSCON(w/r): (XFR 0X0F9F) Power save mode control (default 0X00)

|         | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|---------|---------|---------|-------|-------|-------|-------|

|         | DIL 1 | DIL 0   | DIL 3   | DIL 4   | ысэ   | DIL Z | DIL I | DILU  |

| Name    | -     | SWBSEL2 | SWBSEL1 | SWBSEL0 | CAHEN | -     | -     | -     |

| Default | -     | 0       | 0       | 0       | 0     | -     | -     | -     |

SWBSEL[2:0]

→ Determine the time period CPU switch back from stop mode after switch back condition.

| SWBSEL [2:0] | Delay time after switch back condition. |

|--------------|-----------------------------------------|

| 000          | 2,000 x system clock                    |

| 001          | 20,000 x system clock                   |

| 010          | 40,000 x system clock                   |

| 011          | 100,000 x system clock                  |

| SWBSEL [2:0] | Delay time after switch back condition. |

|--------------|-----------------------------------------|

| 100          | 200,000 x system clock                  |

| 101          | 400,000 x system clock                  |

| 110          | 600,000 x system clock                  |

| 111          | 1,000,000 x system clock                |

CAHEN

- = 1 → Enable internal 1 byte flash cache.

- = 0  $\rightarrow$  Disable internal 1 byte flash cache.

#### 8. CS8959 SFR ALLOCATION

#### 8.1 INTRODUCTION

CS8959 is an ultra high performance, speed optimized 8-bit embedded controller dedicated for operation with fast (typically on-chip) and slow (off-chip) memories. The chip has been designed with a special concern about performance to power consumption ratio. CS8959 is 100% binary-compatible with the industry standard 8051 8-bit micro-controller. The CS8959 is Hardware configure where internal data and program buses are separated. CS8959 has pipelined RISC architecture that is 6.7 times faster in typical applications compared to standard architecture. This performance can also be exploited to great advantage in low power applications where the core can be clocked more slowly than the original implementation for no performance penalty.

#### 8.2 INTERNAL DATA MEMORY & SFRS ALLOCATION

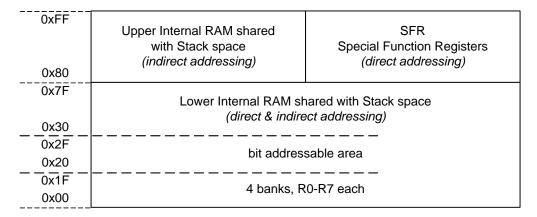

The picture below shows the Internal Memory and Special Function Registers (SFR) map.

Figure-4. SFR Map

The lower internal RAM consists of four register banks with eight registers each, a bit addressable segment with 128 bits (16 bytes) begins at 0X20, and a scratch pad area with 208 bytes. With the indirect addressing mode range 0X80 to 0XFF highest 128 bytes of the internal memory is addressed. With the direct addressing mode range 0X80 to 0XFF the SFR memory area is accessed.

# SFR Memory Map

|      | 0/8   | 1/9    | 2/A    | 3/B    | 4/C    | 5/D    | 6/E      | 7/F     |      |

|------|-------|--------|--------|--------|--------|--------|----------|---------|------|

| 0XF8 | EXIP  | MD0    | MD1    | MD2    | MD3    | MD4    | MD5      | ARCON   | 0XFF |

| 0XF0 | В     |        |        |        | I2CMSA | I2CMCR | I2CMBUF  | I2CMTP  | 0XF7 |

| 0XE8 | EXIE  |        | MXAX   |        | SPICR  | SPIMR  | SPIST    | SPIDATA | 0XEF |

| 0XE0 | ACC   | T2CON5 | RLDL_5 | RLDH_5 | TH2_5  | TL2_5  |          |         | 0XE7 |

| 0XD8 | WDCON | T2CON4 | RLDL_4 | RLDH_4 | TH2_4  | TL2_4  |          |         | 0XDF |

| 0XD0 | PSW   | T2CON3 | RLDL_3 | RLDH_3 | TH2_3  | TL2_3  |          |         | 0XD7 |

| 0XC8 | T2CON | T2MOD  | RCAP2L | RCAP2H | TL2    | TH2    |          |         | 0XCF |

| 0XC0 | SCON1 | SBUF1  |        |        | PMR    | STATUS | Reserved | TA      | 0XC7 |

| 0XB8 | IP    | T2CON2 | RLDL_2 | RLDH_2 | TH2_2  | TL2_2  |          |         | 0XBF |

| 0XB0 | P3    | T2CON1 | RLDL_1 | RLDH_1 | TH2_1  | TL2_1  |          |         | 0XB7 |

| 0XA8 | IE    | T2CON0 | RLDL_0 | RLDH_0 | TH2_0  | TL2_0  |          |         | 0XAF |

| 0XA0 | P2    | P4     | P5     | P6     | P7     | P8     | P9       |         | 0XA7 |

| 0X98 | SCON0 | SBUF0  | DPXR   | ESP    |        | ACON   |          | LVDT    | 0X9F |

| 0X90 | P1    | EXIF   | WTST   | DPX    |        | DPX1   |          |         | 0X97 |

| 0X88 | TCON  | TMOD   | TL0    | TL1    | TH0    | TH1    | CKCON    |         | 0X8F |

| 0X80 | P0    | SP     | DPL    | DPH    | DPL1   | DPH1   | DPS      | PCON    | 0X87 |

|      | 0/8   | 1/9    | 2/A    | 3/B    | 4/C    | 5/D    | 6/E      | 7/F     | _    |

#### Default value:

| Delault | 0/8 | 1/9 | 2/A | 3/B | 4/C | 5/D | 6/E | 7/F |      |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 0XF8    | 00H | 0XFF |

| 0XF0    | 00H |     |     |     | 00H | 00H | 00H | FFH | 0XF7 |

| 0XE8    | 00H |     | 00H |     | 20H | 00H | 00H | 00H | 0XEF |

| 0XE0    | 00H | 00H | 00H | 00H | 00H | 00H |     |     | 0XE7 |

| 0XD8    | 00H | 00H | 00H | 00H | 00H | 00H |     |     | 0XDF |

| 0XD0    | 00H | 00H | 00H | 00H | 00H | 00H |     |     | 0XD7 |

| 0XC8    | 00H | 00H | 00H | 00H | 00H | 00H |     |     | 0XCF |

| 0XC0    | 00H | 00H |     |     | 00H | 00H | 00H | 00H | 0XC7 |

| 0XB8    | 00H | 00H | 00H | 00H | 00H | 00H |     |     | 0XBF |

| 0XB0    | FFH | 00H | 00H | 00H | 00H | 00H |     |     | 0XB7 |

| 0XA8    | 00H | 00H | 00H | 00H | 00H | 00H |     |     | 0XAF |

| 0XA0    | FFH |     | 0XA7 |

| 0X98    | 00H | 00H | 00H | 10H |     | 00H |     | 20h | 0X9F |

| 0X90    | FFH | 00h | 00H | 00H |     | 00H |     |     | 0X97 |

| 0X88    | 00H | 00H | 00H | 00H | 00H | 00H | 03H |     | 0X8F |

| 0X80    | FFH | 07H | 00H | 00H | 00H | 00H | 00H | 00H | 0X87 |

|         | 0/8 | 1/9 | 2/A | 3/B | 4/C | 5/D | 6/E | 7/F |      |

#### 9. SPECIAL SFR DEFINITION

#### 9.1 PROGRAM WAIT STATES REGISTER

Wait States register holds the information about Program Memory access time. It allows the CS8959 core operation with fast (on-chip) and slow (off-chip) Program Memories.

# 9.1.1 Wait-states Cycle Register (default 0X00)

WTST(w/r): (SFR 0X92) Wait-states Cycle Register (default 0X00)

|         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|

| Name    | -     | -     | -     | -     | WTST.3 | WTST.2 | WTST.1 | WTST.0 |

| Default | -     | -     | -     | -     | 0      | 0      | 0      | 0      |

**Note:** These bits are considered during program fetches and MOVC instructions only. Minimal read cycle takes 1 clock period and maximal 16 clock periods

# 9.1.2 WTST Register Values

| WTST value WTST[3:0] | Access time [clk] |

|----------------------|-------------------|

| 15                   | 16                |

| 14                   | 15                |

|                      |                   |

| 1                    | 2                 |

| 0                    | 1                 |

WTST[3:0] should be not less than 1 at this version

#### 9.2 FLAT/LARGE MODEL SWITCHING

Switching between LARGE and FLAT modes is performed by appropriate writes into ACON(0X9D) register. This register is timed access register, prevents from accidental change of working mode.

# 9.2.1 Address Control Register

ACON(w/r): (SFR 0X9D) Address Control Register (default 0X00)

|         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | -     | -     | -     | -     | -     | SA    | AM1   | AM0   |

| Default | -     | -     | -     | -     | -     | 0     | 0     | 0     |

- SA ---- Extend Stack Address Mode indicator. This bit is read only:

- 0 ---- All instructions utilize the 8-bit 8051 stack pointer SP(0X81) resides in internal data memory.

- 1 ----- All instructions utilize the 16-bit stack pointer formed by ESP:SP register (0X9B:OX81). Stack resides in external data memory.

AM[1:0] ----- Address Mode Control bits. These bits establish the addressing mode for the micro controller.

They can only be modified by the Timed access register procedure.

#### 9.2.2 Address Control

| AM[1:0] | Addressing Mode                        |

|---------|----------------------------------------|

| 00      | 16-bit Addressing Mode-LARGE           |

| 1X      | 24-bit contiguous Addressing Mode-FLAT |

- Unimplemented bit. Read as 0 or 1.

To switch between modes the following instructions should be performed:

- MOV TA ,#0XAA

- MOV TA,#0X55

- MOV ACON ,#0X02;Switch to FLAT mode

Or

- MOV TA ,#0XAA

- MOV TA ,#0X55

- MOV ACON,#0X00;Switch to LARGE Mode

# 9.2.3 Stack Pointer Register

SP(w/r): (SFR 0X81) Stack Pointer Register (default 0X03)

|         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | SP.7  | SP.6  | SP.5  | SP.4  | SP.3  | SP.2  | SP.1  | SP.0  |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     |

SP(0X81) register holds the low order 8-bit address used for addressing the Stack Memory. When processor is in LARGE or FLAT mode. After reset SP has 0X07 value.

## **Extended Stack Pointer Register**

ESP(w/r): (SFR 0X9B) Extended Stack Pointer Register (default 0X10)

| Ì       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | ESP.7 | ESP.6 | ESP.5 | ESP.4 | ESP.3 | ESP.2 | ESP.1 | ESP.0 |

| Default | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

ESP(0X9B) register holds the eight high order address bits used for addressing the Stack Memory when processor is in FLAT mode. After reset ESP has 0X00 value.

#### 9.3 DATA POINTER EXTENDED REGISTERS

Data Pointer Extended register DPX, DPX1, MXAX, and DPXR hold the most significant part of memory Address during access to data located above 64 kB in LARGE and FLAT mode. After reset DPX, DPX1, MXAX, DPXR have 0X00 value.

# 9.3.1 Data Pointer Extended Register

DPX(w/r): (SFR 0X93) Data Pointer Extended Register (default 0X00)

| ,       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | DPX.7 | DPX.6 | DPX.5 | DPX.4 | DPX.3 | DPX.2 | DPX.1 | DPX.0 |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

# 9.3.2 Data Pointer Extended 1 Register

DPX1(w/r): (SFR 0X95) Data Pointer Extended 1 Register (default 0X00)

|         | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--|

| Name    | DPX1.7 | DPX1.6 | DPX1.5 | DPX1.4 | DPX1.3 | DPX1.2 | DPX1.1 | DPX1.0 |  |

| Default | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |

## 9.3.3 MOVX @Ri Extended High Register

MXAX(w/r): (SFR 0XEA) MOVX @Ri Extended High Register (default 0X00)

| 11170 134(1171) | . (0 0 | 1, 11.0 171 0. | ti =xtoiiaot | <u> </u> | 10: (0:0:0:0:1 | 07100) |        |        |

|-----------------|--------|----------------|--------------|----------|----------------|--------|--------|--------|

|                 | Bit 7  | Bit 6          | Bit 5        | Bit 4    | Bit 3          | Bit 2  | Bit 1  | Bit 0  |

| Name            | MXAX.7 | MXAX.6         | MXAX.5       | MXAX.4   | MXAX.3         | MXAX.2 | MXAX.1 | MXAX.0 |

| Default         | 0      | 0              | 0            | 0        | 0              | 0      | 0      | 0      |

## 9.3.4 MOVX @Ri Extended Middle Register

DPXR(w/r): (SFR 0X9A) MOVX @Ri Extended Middle Register (default 0X00)

|         | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name    | DPXR.7 | DPXR.6 | DPXR.5 | DPXR.4 | DPXR.3 | DPXR.2 | DPXR.1 | DPXR.0 |

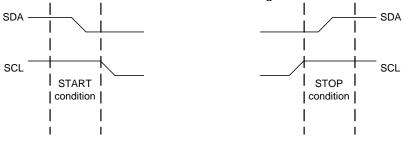

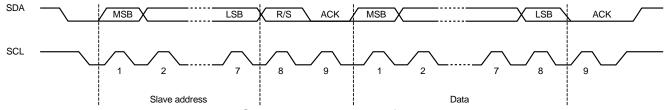

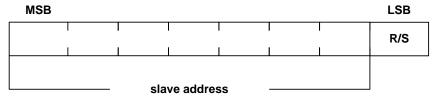

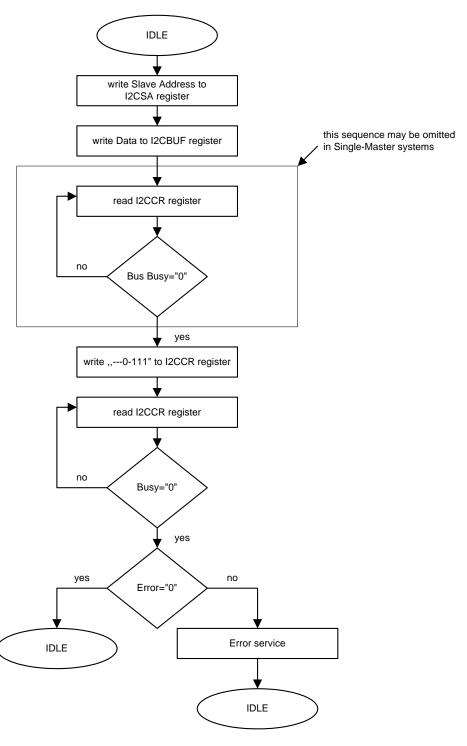

| Default | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |